# Arm Debug and Trace Interface Specification

| TRACE32 Online Help                                 |    |

|-----------------------------------------------------|----|

| TRACE32 Directory                                   |    |

| TRACE32 Index                                       |    |

| TRACE32 Documents                                   | Þ  |

| ICD In-Circuit Debugger                             |    |

| Processor Architecture Manuals                      | Ê  |

| Arm/CORTEX/XSCALE                                   | Þ  |

| Arm Application Notes                               |    |

| Arm Debug and Trace Interface Specification         | 1  |

| History                                             | 5  |

| Introduction                                        | 6  |

| LAUTERBACH Probes                                   | 7  |

| Interface Types, Connectors and LAUTERBACH Probes   | 7  |

| LAUTERBACH Probe Description                        | 11 |

| IDC20A Debug Cable                                  | 11 |

| HS Whisker                                          | 11 |

| AUTO26 Debug Cable                                  | 12 |

| AutoFocus II Preprocessor                           | 12 |

| AutoFocus II MIPI Preprocessor                      | 13 |

| HSSTP Preprocessor                                  | 13 |

| PowerTrace Serial HSSTP                             | 14 |

| Aurora 2 Preprocessor                               | 14 |

| PowerTrace Serial PCIe                              | 15 |

| Debug Interface                                     | 16 |

| Introduction                                        | 16 |

| Three Debug Interface Standards                     | 16 |

| Required Signals                                    | 16 |

| On-Chip Trace                                       | 16 |

| Serial Wire Viewer (SWV) / Serial Wire Output (SWO) | 16 |

| Debug Probe Connectors                              | 17 |

| ARM-20                                              | 17 |

| MIPI-20T                                            | 18 |

| MIPI-10                                             | 19 |

| AUTO-26                                             | 20 |

| MIPI-20D, MIPI-34                                   | 21 |

| Debug Signals                                       | 22 |

| DC Electrical Characteristics                               | 29 |

|-------------------------------------------------------------|----|

| Debug Probe Driver/Receiver (IDC20A)                        | 31 |

| Output Circuitry                                            | 31 |

| Input Circuitry                                             | 31 |

| Debug Probe Driver/Receiver (HS Whisker and AUTO26)         | 33 |

| AC Electrical Characteristics                               | 36 |

| JTAG Timing                                                 | 37 |

| SWD Timing                                                  | 39 |

| Target Design Considerations                                | 41 |

| Electrical                                                  | 41 |

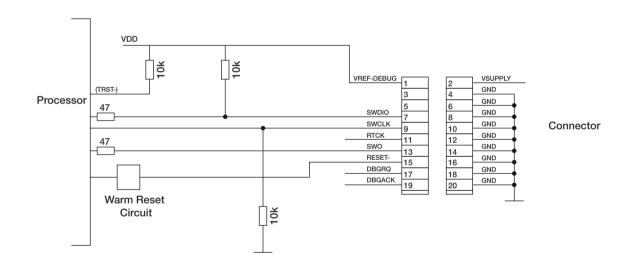

| Example for a JTAG Interface on the Target Board            | 42 |

| Example for a SWD Interface on the Target Board             | 42 |

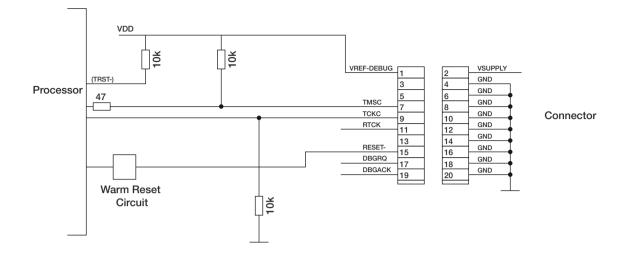

| Example for a cJTAG Interface on the Target Board           | 43 |

| General Recommendations for Debug Connector Placement       | 44 |

| Reset Considerations                                        | 45 |

| RESET- versus TRST-                                         | 45 |

| Debugging from the Very Beginning                           | 45 |

| Debugging a Reset Event                                     | 46 |

| Hot Plugging                                                | 46 |

| Trace Interface                                             | 47 |

| Parallel Trace Interface                                    | 47 |

| Parallel Trace Connector                                    | 47 |

| Mictor-38                                                   | 47 |

| MIPI-60                                                     | 49 |

| Parallel Trace Signals                                      | 51 |

| Serial Trace Interface                                      | 52 |

| Serial Trace Connector                                      | 52 |

| Samtec-40                                                   | 52 |

| Serial Trace Signals                                        | 54 |

| PCIe Trace Interface                                        | 55 |

| PCIe Trace Connector                                        | 55 |

| Samtec-80                                                   | 55 |

| PCIe Trace Signals                                          | 57 |

| Converter                                                   | 59 |

| Cross Converting Table                                      | 59 |

| Cross Converting Table for Manufacturer Specific Connectors | 60 |

| Converter Description                                       | 60 |

| LA-2730 Converter MIPI-20T to IDC20A                        | 60 |

| LA-2770 Converter IDC20A to MIPI-34 PowerTrace Serial       | 60 |

| LA-2774 Converter MIPI-20T to MIPI-34                       | 61 |

| LA-2775 Converter MIPI-20T to MIPI-60                       | 62 |

| LA-2776 Converter MIPI-20T to MICTOR-38                     | 63 |

| LA-2777 Converter MIPI-20T to TI-14                         | 63 |

| LA-3722 Converter IDC20A to Mictor-38                 | 64 |

|-------------------------------------------------------|----|

| LA-3770 Converter IDC20A to MIPI-10/20/34             | 65 |

| LA-3780 Converter IDC20A to TI-14/TI-20-Compact       | 67 |

| LA-3809 Converter Mictor-38/IDC20A to MIPI-20T        | 68 |

| LA-3817 Converter MIPI-60 to Mictor-38                | 68 |

| LA-3818 Converter 2xMictor38/IDC20A to MIPI-60        | 69 |

| LA-3862 Converter IDC20A/MIPI-34 to Mictor-38         | 69 |

| LA-3863 Converter IDC20A to ALTERA-10/RISCV-10        | 70 |

| LA-3880 Conv. ICD20A, MIPI-34, MIPI-60 to 2xMictor-38 | 72 |

| LA-3881 Converter IDC20A to XILINX-14                 | 73 |

| LA-7748 Converter IDC20A to TI-14                     | 73 |

Version 09-May-2024

# History

22-Mar-2024 Fully revised version.

15-Mar-2024 Changed the file name from arm\_app\_jtag.pdf to app\_arm\_target\_interface.pdf.

This application note describes the requirements for seamless compatibility between the debug and trace interface of Arm-based chips and LAUTERBACH tools. It includes specifications for logical functionality, physical connectivity, electrical properties, timing behavior and the design of the printed circuit board (PCB).

The document is intended for:

- Developers looking for guidance on how to connect LAUTERBACH tools to their existing target board.

- Developers of target boards who want to ensure seamless connectivity with LAUTERBACH tools.

- Engineers investigating issues related to an existing interface.

# Interface Types, Connectors and LAUTERBACH Probes

When working with LAUTERBACH tools, you always have access to a debug interface, with the option to additionally utilize a trace interface. Most targets feature a debug connector and, optionally, a trace connector. However, there are also targets where both the debug and trace interfaces are provided by a single connector.

There are three types of debug interface standards for the Arm architecture:

- **JTAG**, IEEE 1149.1

- **SWD**, Serial Wire Debug

- **cJTAG**, Compact JTAG, IEEE 1149.7

LAUTERBACH debug probes consistently support all three types. You can select the interface type supported by your target within the TRACE32 GUI. If your target supports multiple debug interface types, you are free to select among them.

There are both parallel and serial trace interfaces available. If your target exports trace data via a PCIe bus, then a PCIe interface is necessary.

The table below enumerates the common target connectors along with the interface types supported by each connector:

| Target Connector                                                  | Interface Type              |

|-------------------------------------------------------------------|-----------------------------|

| ARM-20                                                            | debug                       |

| MIPI-10                                                           | debug                       |

| MIPI-20T                                                          | debug, 4-bit parallel trace |

| AUTO-26                                                           | debug                       |

| A010-20                                                           | debug                       |

| Mictor-38                                                         | (debug,) parallel trace     |

| MIPI-60                                                           | (debug,) parallel trace     |

| Samtec-40                                                         | (debug,) serial trace       |

| Samtec-80<br>(converter to MiniPCIe, PCIe-Slot x1/x4/x8, OCuLink) | PCIe trace                  |

Further details can be found in chapter "Debug Interface", page 16 and "Trace Interface", page 47.

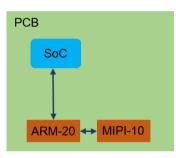

The table before illustrates that in nearly all cases, separate connectors are utilized for debug and trace interfaces. The lone exception is the MIPI-20T connector, which supports both interfaces concurrently.

The trace connectors Mictor-38, MIPI-60, and Samtec-40 can also be used for the debug interface. This not only conserves connectors but also saves space on the target hardware. However, it's important to note that when connecting a Debug Cable or HS Whisker to the target, a converter is necessary, such as ARM-20 to Mictor-38.

To facilitate the use of a common connector, Lauterbach trace probes offer the flexibility of connecting either the Debug Cable or HS Whisker. For details regarding which connector is provided by individual trace probes, please consult the subsequent table. The photo depicts the ARM-20 connector supplied by the trace probes AutoFocus II Preprocessor and the HSSTP Preprocessor.

The subsequent table outlines the probe connectors provided by each LAUTERBACH probe, along with usage hints and important notes. LAUTERBACH provides converters for compatibility if the probe connector does not align with your target connector:

| Probe                                   | Probe<br>Connector | Usage Hints                                                                 | Note                                                                                        |

|-----------------------------------------|--------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| IDC20A<br>Debug Cable                   | ARM-20             | robust debug<br>connector                                                   |                                                                                             |

| HS Whisker<br>(μTrace or<br>CombiProbe) | MIPI-20T           | small debug<br>connector with 4-bit<br>low bandwidth<br>parallel trace port | trace bandwidth is sufficient for<br>most Cortex-M cores or system<br>trace such as ITM/STM |

|                                         | MIPI-10            | smallest debug<br>connector                                                 |                                                                                             |

| Probe                                | Probe<br>Connector | Usage Hints                                                                                                     | Note                                                                                                                                                                                                                                                     |

|--------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUTO26<br>Debug Cable                | AUTO-26            | only use this debug<br>connector if<br>concurrent use is<br>required                                            | facilitates concurrent utilization of<br>the debug interface by a<br>calibration tool (automotive<br>sector)                                                                                                                                             |

|                                      | MIPI-20T           | small debug<br>connector                                                                                        | unlike HS Whisker, the trace pins<br>cannot be used<br>the primary tool used with this<br>connector is the HS Whisker                                                                                                                                    |

|                                      | MIPI-10            | small debug<br>connector                                                                                        | the primary tool used with this connector is the HS Whisker                                                                                                                                                                                              |

| AutoFocus II<br>Preprocessor         | Mictor-38          | robust parallel trace<br>connector<br>single Mictor-38 for<br>up to 16 bit<br>two Mictor-38 for up<br>to 32 bit | Mictor-38 connector is the<br>preferred connector for parallel<br>trace ports<br>enables an ARM-20 connection<br>when the debug interface is also<br>utilized through the Mictor-38<br>connector                                                         |

| AutoFocus II<br>MIPI<br>Preprocessor | MIPI-60            | parallel trace<br>connector for up to<br>32 bit                                                                 | typically used with Texas<br>Instruments evaluation boards<br>enables a MIPI34 connection<br>when the debug interface is also<br>utilized through the MIPI-60<br>connector                                                                               |

| HSSTP<br>Preprocessor                | Samtec-40          | serial trace<br>connector,<br>up to 4 lanes                                                                     | outdated probe, should only be<br>utilized if PowerTrace II/III is<br>accessible and the lower<br>bandwidth meets the<br>requirements<br>enables an ARM-20 connection<br>when the debug interface is also<br>utilized through the Samtec-40<br>connector |

| Probe                                                            | Probe<br>Connector | Usage Hints                                                             | Note                                                                                                                                 |

|------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| PowerTrace<br>Serial<br>HSSTP                                    | Samtec-40          | serial trace<br>connector,<br>up to 6 lanes (8 lanes<br>with Samtec-80) | standard solution<br>enables an MIPI34 connection<br>when the debug interface is also<br>utilized through the Samtec-40<br>connector |

| Aurora 2<br>Preprocessor<br>connected to<br>PowerTrace<br>Serial | Samtec-40          | serial trace<br>connector,<br>up to 4 lanes at<br>higher speed          |                                                                                                                                      |

| PowerTrace<br>Serial<br>PCIe                                     | Samtec-80          | serial trace<br>connector,<br>up to 8 lanes                             | typically used with converter for<br>PCIe slots or OKuLink connector<br>on the target                                                |

This chapter provides an introduction to the individual Lauterbach probes. It includes a photograph depicting the probe within a fully operational TRACE32 tool configuration. Additionally, details regarding the probe connector and the supported interface type are provided.

# **IDC20A Debug Cable**

Picture: ICD20A Debug Cable on a PowerDebug base module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug modules along with their respective delivery periods.

#### Connector: ARM-20

Interface type: debug

**Dimension:** A drawing illustrating the dimensions of the IDC20A Debug Cable is available at www2.lauterbach.com/size/si\_3000.pdf.

## **HS Whisker**

Picture: HS Whisker on CombiProbe 2 connected to a PowerDebug base module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug modules along with their respective delivery periods.

Connector: MIPI-10, MIPI-20T, both via the included matching cable

Interface type: debug, optional 4 bit parallel trace (only with MIPI-20T)

Picture: AUTO26 Debug Cable connected to a PowerDebug base module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug modules along with their respective delivery periods.

Connector: MIPI-10, MIPI-20T, AUTO26, all via the included matching cable

Interface type: debug

# AutoFocus II Preprocessor

**Picture:** AutoFocus II Preprocessor connected to PowerTrace module and IDC20A Debug Cable connected to PowerDebug module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug and PowerTrace modules along with their respective delivery periods.

Connector: Mictor-38 via the included Mictor flex extension

Interface type: (debug), parallel trace

**Dimension:** A drawing illustrating the dimensions of the Mictor-38 flex extension is available at www2.lauterbach.com/size/si\_1370.pdf.

**Picture:** AutoFocus II MIPI Preprocessor connected to PowerTrace module and IDC20A Debug Cable connected to PowerDebug module.

The chapter "TRACE32 Product Story" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug and PowerTrace modules along with their respective delivery periods.

Connector: MIPI-60 via the included flex extension for Samtec-60

Interface type: (debug,) parallel trace

**Dimension:** A drawing illustrating the dimensions of the Samtec-60 flex extension is available at www2.lauterbach.com/size/si\_1228.pdf.

## **HSSTP** Preprocessor

**Picture:** HSSTP Preprocessor connected to PowerTrace module and IDC20A Debug Cable connected to PowerDebug module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug and PowerTrace modules along with their respective delivery periods.

Connector: Samtec-40 via included flex extension for Samtec-40

Interface type: (debug,) serial trace

**Dimension:** A drawing illustrating the dimensions of the Samtec-40 flex extension is available at www2.lauterbach.com/size/si\_1232.pdf.

# PowerTrace Serial HSSTP

Picture: PowerTrace Serial and IDC20A Debug Cable connected to PowerDebug module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug and PowerTrace modules along with their respective delivery periods.

Connector: Samtec-40 via included flex extension for Samtec-40

Interface type: (debug,) serial trace

## Aurora 2 Preprocessor

**Picture:** Aurora 2 Preprocessor connected to a PowerTrace Serial, IDC20A Debug Cable connected to PowerDebug module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug and PowerTrace modules along with their respective delivery periods.

Connector: Samtec-40 via included flex extension for Samtec-40

Interface type: serial trace

Picture: PowerTrace Serial and IDC20A Debug Cable connected to PowerDebug module.

The chapter "**TRACE32 Product Story**" in TRACE32 Terminology, page 9 (trace32\_terms.pdf) outlines the various versions of the PowerDebug and PowerTrace modules along with their respective delivery periods.

Connector: Samtec-80 via included flex extension for Samtec-80

Interface type: PCle trace

**Picture:** Converters from Samtec-80 to PCIe-Slot x1 (LA-3527), PCIe-Slot x4 (LA-3524), PCIe-Slot x8 (LA-3525), MiniPCIe (LA-3526), OCuLink (LA-3590+LA-1990), PCIe-Slot x4 or OCuLink with PCIe Gen 4 Preprocessor (LA-3529).

Connector: PCIe-Slot x1/x4/x8, MiniPCIe, OCuLink (description see industry standard)

Interface type: PCIe trace

# Introduction

# Three Debug Interface Standards

Three standards can be used for the debug interface:

- **JTAG**, IEEE 1149.1

- **SWD**, Serial Wire Debug, an Arm standard

- **cJTAG**, Compact JTAG, IEEE 1149.7

cJTAG is seldom utilized and not advisable if alternatives like JTAG or SWD are available, as it operates significantly slower.

All debug connectors and all our debug probes support JTAG, SWD and cJTAG. The JTAG signals TCK and TMS are reused for SWD and cJTAG. The following interface description therefore covers all three interfaces at once.

## **Required Signals**

Depending on the standard used, you will need in addition to VREF-DEBUG and GND:

- JTAG: TCK, TMS, TDI, TDO, (TRST-)

- SWD: SWCLK, SWDIO, (SWO)

- cJTAG: TCKC, TMSC

It is recommended that you also use RESET-.

## **On-Chip Trace**

The debug interface is also sufficient for on-chip trace, as the trace recording is stored in real time in a memory on the chip and the trace data is read out more slowly via the debug interface after recording.

# Serial Wire Viewer (SWV) / Serial Wire Output (SWO)

Further Arm's one-pin-trace port called Serial Wire Viewer (SWV) / Serial Wire Output (SWO) is described together with our debug interface here, because the JTAG signal TDO is re-used for that purpose. So, pinout and electrical specification is the same as for JTAG/TDO. SWV/SWO is supported by all newer debug probes and newer base modules, i.e. HS Whisker on µTrace or CombiProbe, AUTO26 Debug Cable version V2 or newer (delivered from 2021), IDC20A Debug Cable version V5 or newer (delivered from 2018) and base modules such as PowerDebug PRO/E40/X50 or newer models. SWV/SWO is typically found on small Cortex-M-based microcontrollers with a small number of pins.

#### ARM-20

#### Pinout:

| Signal         | Pin | Pin | Signal             |

|----------------|-----|-----|--------------------|

| VREF-DEBUG     | 1   | 2   | VSUPPLY (not used) |

| TRST-          | 3   | 4   | GND                |

| TDI            | 5   | 6   | GND                |

| TMSITMSCISWDIO | 7   | 8   | GND                |

| TCKITCKCISWCLK | 9   | 10  | GND                |

| RTCK           | 11  | 12  | GND                |

| TDOI-ISWO      | 13  | 14  | GND                |

| RESET-         | 15  | 16  | GND                |

| DBGRQ          | 17  | 18  | GND                |

| DBGACK         | 19  | 20  | GND                |

For a comprehensive description of all signals displayed in the pinouts, refer to the "**Debug Signals**", page 22.

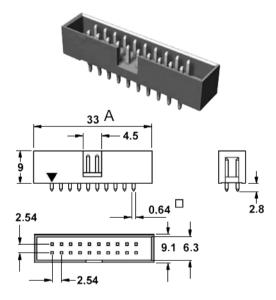

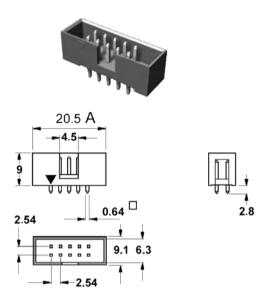

#### **Target Connector:**

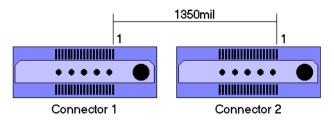

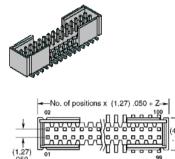

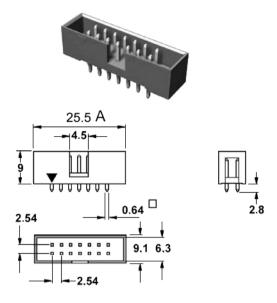

The target board requires a standard 20 pin double row male connector, pin to pin spacing 2.54mm/0.100" x 2.54mm/0.100" and 0.025" square post width. A shrouded connector with center polarization is recommended.

#### Placement:

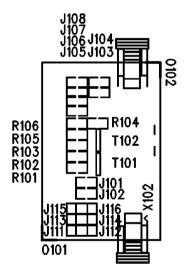

Please refer to the general recommendations outlined in the chapter "General Recommendations for Debug Connector Placement", page 44.

We recommend placing the even numbered pins on the edge of the board (probe flex cable won't get twisted).

**Examples with housing:** Samtec HTST-110-01-L-D (through-hole), Samtec HTST-110-01-L-DV (surface mount)

Examples without housing: Samtec TSW-110-23-L-D, Berg: 67996-120H

#### **MIPI-20T**

MIPI-20T is equivalent to Arm's "CoreSight 20", except that MIPI-20T has pins 11 and 13 connected to GND (instead of N/C).

#### Pinout:

| Signal     | Pin | Pin | Signal         |

|------------|-----|-----|----------------|

| VREF-DEBUG | 1   | 2   | TMSITMSCISWDIO |

| GND        | 3   | 4   | TCKITCKCISWCLK |

| GND        | 5   | 6   | TDOI-ISWO      |

| GND (KEY)  | -   | 8   | TDI            |

| GND        | 9   | 10  | RESET-         |

| GND        | 11  | 12  | TRACECLK       |

| GND        | 13  | 14  | TRACEDATA[0]   |

| GND        | 15  | 16  | TRACEDATA[1]   |

| GND        | 17  | 18  | TRACEDATA[2]   |

| GND        | 19  | 20  | TRACEDATA[3]   |

For a comprehensive description of all signals displayed in the pinouts, refer to the "**Debug Signals**", page 22.

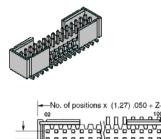

#### **Target Connector:**

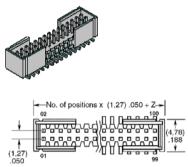

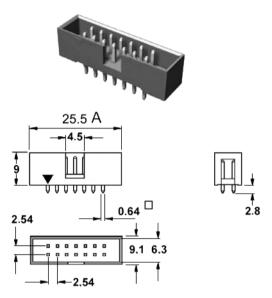

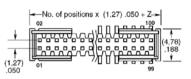

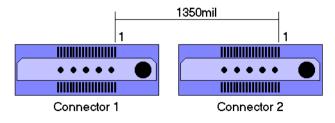

The target board requires a 20 pin double row male connector with 1.27mm/0.050" x 1.27mm/0.050" pin to pin spacing and 0.016" square post width. A shrouded connector with center polarization is recommended. Pin 7 is a key pin that prevents mating in the wrong orientation. Therefore, pin 7 must be removed on the target side.

#### Placement:

Please refer to the general recommendations outlined in the chapter "General Recommendations for Debug Connector Placement", page 44.

We recommend placing the odd numbered pins on the edge of the board (probe flex cable won't get twisted).

Example with housing: Samtec FTSH-110-01-L-DV-K (surface mount)

#### MIPI-10

MIPI-10 is equivalent to Arm's "CoreSight 10".

#### Pinout:

| Signal     | Pin | Pin | Signal         |

|------------|-----|-----|----------------|

| VREF-DEBUG | 1   | 2   | TMSITMSCISWDIO |

| GND        | 3   | 4   | TCKITCKCISWCLK |

| GND        | 5   | 6   | TDOI-ISWO      |

| GND (KEY)  | -   | 8   | TDI            |

| GND        | 9   | 10  | RESET-         |

For a comprehensive description of all signals displayed in the pinouts, refer to the "Debug Signals", page 22.

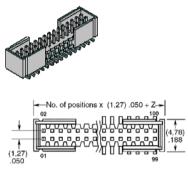

#### **Target Connector:**

The target board requires a 10 pin double row male connector with 1.27mm/0.050" x 1.27mm/0.050" pin to pin spacing and 0.016" square post width. A shrouded connector with center polarization is recommended. Pin 7 is a key pin that prevents mating in the wrong orientation. Therefore, pin 7 must be removed on the target side.

#### Placement:

Please refer to the general recommendations outlined in the chapter "General Recommendations for Debug Connector Placement", page 44.

We recommend placing the odd numbered pins on the edge of the board (probe flex cable won't get twisted).

Example with housing: Samtec FTSH-105-01-L-DV-K (surface mount)

#### **AUTO-26**

#### Pinout:

| Signal     | Pin | Pin | Signal         |

|------------|-----|-----|----------------|

| VREF-DEBUG | 1   | 2   | TMSITMSCISWDIO |

| GND        | 3   | 4   | TCKITCKCISWCLK |

| GND        | 5   | 6   | TDOI-ISWO      |

| GND (KEY)  | -   | 8   | TDI            |

| GND        | 9   | 10  | RESET-         |

| GND        | 11  | 12  | RTCK           |

| GND        | 13  | 14  | TRST- PULLDOWN |

| GND        | 15  | 16  | TRST-          |

| GND        | 17  | 18  | DBGRQ (EMU0)   |

| GND        | 19  | 20  | DBGACK (EMU1)  |

| GND        | 21  | 22  | BREQ-          |

| GND        | 23  | 24  | BGRNT-         |

| GND        | 25  | 26  | EXTIO          |

For a comprehensive description of all signals displayed in the pinouts, refer to the "Debug Signals", page 22.

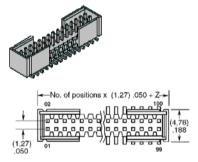

#### **Target Connector:**

The target board requires a 26 pin double row male connector with 1.27mm/0.050" x 1.27mm/0.050" pin to pin spacing and 0.016" square post width. A shrouded connector with center polarization is recommended. Pin 7 is a key pin that prevents mating in the wrong orientation. Therefore, pin 7 must be removed on the target side.

#### Placement:

Please refer to the general recommendations outlined in the chapter "General Recommendations for Debug Connector Placement", page 44.

We recommend placing the odd numbered pins on the edge of the board (probe flex cable won't get twisted).

Example with housing: Samtec FTSH-113-01-L-DV-K (surface mount)

#### MIPI-20D, MIPI-34

These two debug probe connectors are outdated and are not described in this manual. Previously, for the CombiProbe, there was a MIPI34 Whisker and corresponding converters available.

- The AutoFocus II MIPI Preprocessor still features a MIPI-34 connector in case the MIPI-60 connector on the target is also used for the debug interface.

- The PowerTrace Serial still features a MIPI-34 connector in case the Samtec-40 connector on the target is utilized for the debug interface.

Both tools come with a converter for ARM20/IDC20A to MIPI-34 (see **converter for ARM-20**). In the event that you are using an HS Whisker, there is a MIPI-20T to MIPI-34 converter available (LA-2774).

The MIPI-20T trace signals are described in chapter "Trace Interface", page 47. VREF-DEBUG is used as the trace voltage reference on this connector (same voltage reference as debug).

If you do not need or wish to utilize any of the signals outlined below, we advise against connecting them. Each signal is terminated on the Lauterbach probe side. Please refrain from using any signal for alternative purposes, as it is connected to drivers/receivers on the Lauterbach probe side. Only VSUPPLY is not connected to the Lauterbach probes.

| Signal /<br>Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Compliance                                                                                                                            | Recommendation                                                                                                           |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| BGRNT-<br>to<br>debugger  | The "Bus Grant" (low active)<br>signal grants the interface usage<br>when employed alongside another<br>tool, such as a calibration tool.                                                                                                                                                                                                                                                                                                                    | Exclusive to<br>AUTO-26.<br>Only<br>necessary<br>when<br>sharing the<br>debug<br>interface,<br>such as with<br>a calibration<br>tool. | Only necessary when<br>sharing the debug interface,<br>such as with a calibration<br>tool.<br>Otherwise, do not connect. |

| BREQ-<br>from<br>debugger | "Bus Request" (low active)<br>requests the interface for use<br>when it is used together with<br>another tool such as a calibration<br>tool.                                                                                                                                                                                                                                                                                                                 | Only with<br>AUTO-26.<br>Only<br>necessary<br>when<br>sharing the<br>debug<br>interface,<br>such as with<br>a calibration<br>tool.    | Only necessary when<br>sharing the debug interface,<br>such as with a calibration<br>tool.<br>Connect to GND otherwise.  |

| DBGACK<br>to<br>debugger  | <ul> <li>"Debug Acknowledge" (active high) serves as an input for the debugger to detect the processor's halt status.</li> <li>However, this signal is largely absent in modern chips.</li> <li>Synchronous halting is typically achieved through an internal cross-trigger matrix (CTI/CTM) within the chip.</li> <li>If accessible, it can be utilized for rapid triggering, such as synchronously halting all chips within a multichip system.</li> </ul> | Is typically<br>unnecessary.                                                                                                          | Do not connect.                                                                                                          |

| Signal /<br>Direction        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Compliance                                | Recommendation                                                                                                                                                  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBGRQ<br>from<br>debugger    | The "Debug Request" (active-<br>high) signal serves as an output<br>from the debugger, aimed at<br>transitioning the processor into<br>debug mode, thereby stopping<br>program execution. While the<br>debugger offers alternative<br>methods to stop program<br>execution, initiating a "Debug<br>Request" remains the fastest<br>approach.<br>However, this signal is largely<br>absent in modern chips.<br>Synchronous halting is typically<br>achieved through an internal<br>cross-trigger matrix (CTI/CTM)<br>within the chip. | Not required<br>anymore.                  | Do not connect.<br>If this signal is provided by<br>the processor you should<br>pull it down on the target<br>side to keep the signal in<br>the inactive state. |

| EXTIO<br>from/to<br>debugger | "External IO". This is a software<br>configurable input/output.<br>Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                          | Exclusive to<br>AUTO-26.<br>Not required. | Do not connect.                                                                                                                                                 |

| GND                          | "Ground".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Mandatory.                                | Connect all GND pins to minimize noise interference.                                                                                                            |

| GND<br>(KEY)                 | This pin serves as a key to prevent<br>incorrect connection of the debug<br>probe to the target hardware. It<br>should be physically cut off on the<br>target connector and is already<br>blocked on the LAUTERBACH<br>probe upon delivery.                                                                                                                                                                                                                                                                                          | Recommen-<br>ded.                         | No electrical function.<br>Protection against incorrect<br>connection.                                                                                          |

| Signal /<br>Direction         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Compliance            | Recommendation                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

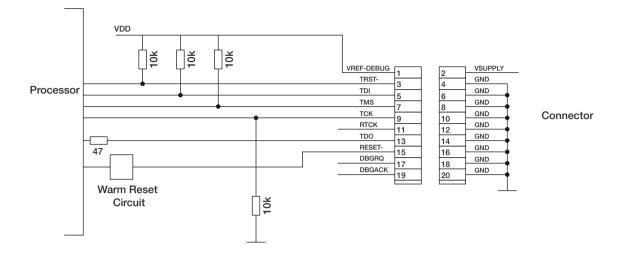

| RESET-<br>from/to<br>debugger | The "System Reset" signal (low active) is used to reset the target system. Additionally, the debugger uses this signal to determine whether the processor is held in reset. This functionality is not mandatory. If the current reset status is not signaled via this line, this pin should be continuously high (= no reset). The debugger controls this pin as an open-drain output (in contrast to other outputs, which are push-pull). A 47 k $\Omega$ pull-up resistor is located inside the debug probe.<br>See important notes in chapter "Reset Considerations", page 45. | Optional.             | Recommended.<br>It may be necessary to<br>include a pull-up resistor<br>$(1 \ k\Omega - 47 \ k\Omega)$ on the<br>target side to prevent<br>unintended resets when the<br>debugger is disconnected.<br>Additionally, it might be<br>advisable to strengthen the<br>weak 47 k\Omega pull-up in the<br>debug probe.                              |

| RTCK<br>to<br>debugger        | "Return Test Clock" was used to<br>synchronize the JTAG signals with<br>the internal clocks of some older<br>ARM7, ARM9 and ARM11 cores.<br>This is not required for CoreSight<br>and/or Cortex cores.                                                                                                                                                                                                                                                                                                                                                                            | Not required anymore. | Do not connect.<br>Especially avoid connecting<br>it to TCK, as this creates a<br>stub on the TCK line, a<br>common source of signal<br>issues we often encounter<br>on customer boards.                                                                                                                                                      |

| SWCLK<br>from<br>debugger     | "Serial Wire Clock" is the SWD clock signal from debugger to processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Required for<br>SWD.  | You should place a pull-down resistor (1 k $\Omega$ - 47 k $\Omega$ ) on this line in order to give it a defined state when the line is not driven by the debugger.                                                                                                                                                                           |

| SWDIO<br>from/to<br>debugger  | "Serial Wire Data I/O" is the SWD<br>data signal from debugger to<br>processor and vice versa.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Required for<br>SWD.  | You can place a 47 $\Omega$<br>series resistor near the<br>processor for the serial<br>termination, if the chip's<br>output driver is not<br>impedance matched. You<br>can place a pull-up resistor<br>(1 k $\Omega$ - 47 k $\Omega$ ) on this line in<br>order to give it a defined<br>state when the line is not<br>driven by the debugger. |

| Signal /<br>Direction    | Description                                                                                                                                                                                            | Compliance                                                          | Recommendation                                                                                                                                                                                                                                                          |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWO<br>to<br>debugger    | The "Serial Wire Output" is an<br>optional single-pin asynchronous<br>trace port with very low bandwidth.<br>It can be utilized alongside the<br>SWD interface, provided that the<br>chip supports it. | Required only<br>if SWO is<br>available and<br>intended for<br>use. | You can place a 47 $\Omega$<br>series resistor near the<br>processor for the serial<br>termination, if the chip's<br>output driver is not<br>impedance matched. You<br>can place a pull-up (or pull-<br>down) resistor (1 k $\Omega$ -<br>47 k $\Omega$ ) on this line. |

| TCK<br>from<br>debugger  | "Test Clock" is the JTAG clock<br>signal from debugger to<br>processor.                                                                                                                                | Required for<br>JTAG.                                               | You should place a pull-<br>down resistor (1 k $\Omega$ - 47 k $\Omega$ ) on this line in order to give<br>it a defined state when the<br>line is not driven by the<br>debugger.                                                                                        |

| TCKC<br>from<br>debugger | "Test Clock Compact" is the cJTAG clock signal from debugger to processor.                                                                                                                             | Required for cJTAG.                                                 | You should place a pull-down resistor (1 k $\Omega$ - 47 k $\Omega$ ) on this line in order to give it a defined state when the line is not driven by the debugger.                                                                                                     |

| TDI<br>from<br>debugger  | "Test Data In" is the JTAG data signal from debugger to processor.                                                                                                                                     | Required for JTAG.                                                  | You can place a pull-up (or pull-down) resistor (1 k $\Omega$ - 47 k $\Omega$ ) on this line in order to give it a defined state when the line is not driven by the debugger.                                                                                           |

| TDO<br>to<br>debugger    | "Test Data Out" is the JTAG data<br>signal from processor to<br>debugger.                                                                                                                              | Required for<br>JTAG.                                               | You can place a 47 $\Omega$<br>series resistor near the<br>processor for the serial<br>termination, if the chip's<br>output driver is not<br>impedance matched. You<br>can place a pull-up (or pull-<br>down) resistor (1 k $\Omega$ -<br>47 k $\Omega$ ) on this line. |

| TMS<br>from<br>debugger  | "Test Mode Select" is the JTAG<br>control signal for the TAP<br>controller.                                                                                                                            | Required for<br>JTAG.                                               | You can place a pull-up resistor (1 k $\Omega$ - 47 k $\Omega$ ) on this line in order to give it a defined state when the line is not driven by the debugger.                                                                                                          |

| Signal /<br>Direction       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Compliance                                                                                                                                   | Recommendation                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMSC<br>from/to<br>debugger | "Test Mode Select Compact" is the<br>cJTAG data signal from debugger<br>to processor and vice versa.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Required for<br>cJTAG                                                                                                                        | You can place a 47 $\Omega$<br>series resistor near the<br>processor for the serial<br>termination, if the chip's<br>output driver is not<br>impedance matched. You<br>can place a pull-up resistor<br>(1 k $\Omega$ - 47 k $\Omega$ ) on this line<br>in order to give it a defined<br>state when the line is not<br>driven by the debugger. |

| TRST-<br>from<br>debugger   | <ul> <li>"Test Reset" (low active) is used<br/>for an asynchronous reset of the<br/>JTAG Test Access Port (TAP). It<br/>resets the TAP state machine.</li> <li>The debugger controls this signal<br/>using a push-pull driver. From the<br/>debugger's perspective, this<br/>signal is optional, as it can<br/>alternatively reset the TAP using a<br/>specific JTAG sequence.</li> <li>A pull-down on target side is not<br/>JTAG compliant, but ensures that<br/>the on-chip debug logic is inactive<br/>if the debugger is not connected.</li> <li>See important notes in chapter<br/>"Reset Considerations", page<br/>45.</li> </ul> | Only with<br>JTAG.<br>Optional if<br>TRST- has a<br>pull-up on<br>target side.<br>Required if<br>TRST- has a<br>pull-down on<br>target side. | Recommended to connect if<br>the chip provides this signal;<br>otherwise, leave it<br>unconnected.<br>You should place a pull-up<br>(or pull-down) resistor (1 k $\Omega$<br>- 47 k $\Omega$ ) on this signal in<br>order to give it a defined<br>state when the signal is not<br>driven by the debugger.                                     |

| Signal /<br>Direction                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Compliance                                                                                                                                   | Recommendation                                                                                                                                                                                                                                                                                         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRST-<br>PULL<br>DOWN<br>from<br>debugger | <ul> <li>"Test Reset" (low active) is used<br/>for an asynchronous reset of the<br/>JTAG Test Access Port (TAP). It<br/>resets the TAP state machine.</li> <li>This signal shall be used instead<br/>of TRST- if there is a pull-down on<br/>this line on the target side,<br/>although the function is identical.</li> <li>The debugger controls it via a<br/>push-pull driver. From the<br/>debugger's point of view, it is<br/>optional, as it also resets the TAP<br/>using a specific JTAG sequence.</li> <li>A pull-down on target side is not<br/>JTAG compliant, but ensures that<br/>the on-chip debug logic is inactive<br/>if the debugger is not connected.</li> <li>See important notes in chapter<br/>"Reset Considerations", page<br/>45.</li> </ul> | Only with<br>JTAG.<br>Optional if<br>TRST- has a<br>pull-up on<br>target side.<br>Required if<br>TRST- has a<br>pull-down on<br>target side. | Recommended if the chip provides this signal, otherwise leave unconnected. You should place a pull-up (or pull-down) resistor ( $1 \ k\Omega - 47 \ k\Omega$ ) on this line in order to give it a defined state when the line is not driven by the debugger.                                           |

| VREF-<br>DEBUG<br>to<br>debugger          | "Voltage Reference Debug" is the<br>target reference voltage for the<br>debug signals.<br>This line indicates the presence of<br>target power. It serves to establish<br>the logic level reference (VREF/2)<br>for the debugger input<br>comparators and automatically<br>adjusts the voltage levels of the<br>debugger output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                             | Required.                                                                                                                                    | It should be directly<br>connected to the power<br>supply of the processor's IO<br>pins. While a series resistor<br>is permissible, it is not<br>advisable. The signal must<br>be robust enough to<br>overpower an<br>approximately $10 \text{ k}\Omega$ pull-<br>down resistor in the debug<br>probe. |

| VSUPPLY<br>to<br>debugger                 | Other debuggers utilize "Voltage<br>Supply" to source their supply<br>current. However, LAUTERBACH<br>debug probes have their own<br>dedicated power supply and do<br>not rely on this feature. As such,<br>this line is not utilized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Not used by<br>LAUTER-<br>BACH debug<br>probes.                                                                                              | Do not connect.<br>For powering non-<br>LAUTERBACH debug tools,<br>you may connect this signal<br>directly to a 5 V or 3.3 V<br>power supply, without the<br>use of a series resistor.                                                                                                                 |

The following table describes the DC electrical characteristics of the debug probes. The current values are measured in the positive direction from the debug probe to the target system. The characteristics apply to the full operating range of the target system. The following values are for reference only and are not guaranteed by LAUTERBACH.

| Symbol | Descrip-<br>tion              | Condition                                                                                  | Min. | Тур.                             | Max.                              | Unit |

|--------|-------------------------------|--------------------------------------------------------------------------------------------|------|----------------------------------|-----------------------------------|------|

| Vvref  |                               | IDC20A                                                                                     | 0.38 |                                  | 5.25                              | V    |

|        | DEBUG<br>operating<br>voltage | HS Whisker                                                                                 | 1.8  |                                  | 5.25                              | V    |

|        | voltage                       | AUTO26                                                                                     | 1.2  |                                  | 5.25                              | V    |

| Vvref_ | VREF-                         | IDC20A                                                                                     | -0.3 | 0.27                             | 0.35                              | V    |

| pwrdwn | DEBUG<br>power<br>down        | HS Whisker                                                                                 | -0.3 | 0.8                              | 0.9                               | V    |

|        | indication                    | AUTO26                                                                                     | -0.3 | 1.65                             | 1.75                              | V    |

| lvref  | VREF-<br>DEBUG<br>current     | Vvref = 5.25V<br>IDC20A<br>HS Whisker<br>AUTO26                                            |      | -0.05<br>-0.525<br>-0.525        | -0.1<br>-0.53<br>-0.53            | mA   |

| Vil    | Low-level<br>input<br>voltage | IDC20A<br>Vvref = 1.5V<br>Vvtef = 1.8V<br>Vvtef = 2.5V<br>Vvref = 3.3V<br>Vvref = 5.0V     | -0.3 | 0.6<br>0.75<br>1.1<br>1.5<br>2.3 | 0.3 * Vvref                       | V    |

|        |                               | HS Whisker<br>Vvref = 1.2V<br>Vvtef = 1.8V<br>Vvref = 2.5V<br>Vvref = 3.3V<br>Vvref = 5.0V | -0.3 |                                  | 0.24<br>0.63<br>0.7<br>0.8<br>1.5 | V    |

|        |                               | AUTO26<br>Vvref = 1.8V<br>Vvref = 2.5V<br>Vvref = 3.3V<br>Vvref = 5.0V                     | -0.3 |                                  | 0.63<br>0.7<br>0.8<br>1.5         | V    |

| Symbol | Descrip-<br>tion                | Condition                                                                                            | Min.                              | Тур.                            | Max.        | Unit |

|--------|---------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|-------------|------|

| Vih    | High-level<br>input<br>voltage  | IDC20A<br>Vvref = 1.5V<br>Vvref = 1.8V<br>Vvref = 2.5V<br>Vvref = 3.3V<br>Vvref = 5.0V               | 0.7 * Vvref                       | 0.9<br>1.0<br>1.4<br>1.8<br>2.6 | 5.25        | V    |

|        |                                 | HS Whisker<br>Vvref = $1.2V$<br>Vvref = $1.8V$<br>Vvref = $2.5V$<br>Vvref = $3.3V$<br>Vvref = $5.0V$ | 0.96<br>1.17<br>1.7<br>2.0<br>3.5 |                                 | 5.25        | V    |

|        |                                 | AUTO26<br>Vvref = 1.8V<br>Vvref = 2.5V<br>Vvref = 3.3V<br>Vvref = 5.0V                               | 1.17<br>1.7<br>2.0<br>3.5         |                                 | 5.25        | V    |

| Vol    | Low-level<br>output<br>voltage  |                                                                                                      | 0                                 | (1)                             | 0.3 * Vvref | V    |

| Voh    | High-level<br>output<br>voltage |                                                                                                      | 0.7* Vvref                        | (1)                             | Vvref       | V    |

| lil    | Low-level<br>input<br>current   |                                                                                                      |                                   |                                 | 0.2         | mA   |

| lih    | High-level<br>input<br>current  |                                                                                                      |                                   |                                 | -0.2        | mA   |

| lol    | Low-level<br>output<br>current  | Vvref < 1.5V<br>Vvref >= 1.5V<br>Vol < 0.3*Vvref                                                     |                                   |                                 | -2<br>-6    | mA   |

| loh    | High-level<br>output<br>current | Vvref < 1.5V<br>Vvref >= 1.5V<br>Voh ><br>0.7*Vvref                                                  |                                   |                                 | 2<br>6      | mA   |

| Symbol                                                                                                                                                                                                                                                                                           | Descrip-<br>tion | Condition  | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|------|------|------|------|

| Rreset                                                                                                                                                                                                                                                                                           | RESET- pin       | IDC20A     |      | 47   |      | kΩ   |

|                                                                                                                                                                                                                                                                                                  | pullup (2)       | HS Whisker |      | 220  |      | kΩ   |

|                                                                                                                                                                                                                                                                                                  |                  | AUTO26     |      | 10   |      | kΩ   |

| (1) Typical value dominated by 47 $\Omega$ series resistor between driver and debug cable. For example, at Iol = -6 mA or Ioh = 6 mA, expect a 0.3 V drop relative to GND or Vvref potential.<br>(2) An additional pull-up on target side might be required if target operation without attached |                  |            |      |      |      |      |

# debugger is desired.

# Debug Probe Driver/Receiver (IDC20A)

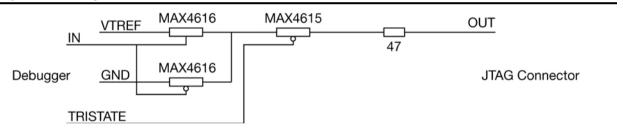

This chapter describes the actual driver/receiver circuit inside the IDC20A Debug Cable. For additional information, refer to the MAX4616, MAX4615 and DS90C032 data sheets.

# **Output Circuitry**

The output signals TCK, TMS, TDI, TRST-, DBGRQ are controlled by analog switches that switch the signal level to VREF-DEBUG (supplied by the debugger), GND, respectively. Another analog switch is used to tristate this output signal. A 47  $\Omega$  resistor is used for current limiting and serial termination. RESET- has a 47 k $\Omega$  pull-up instead of the analog switch to VREF-DEBUG (see Input Circuitry).

# **Input Circuitry**

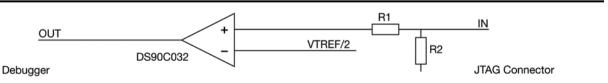

The input signals TDO, RTCK, DBGACK, RESET- are compared to VREF-DEBUG/2.

| Signal | R1  | R2                                                                       |

|--------|-----|--------------------------------------------------------------------------|

| RTCK   | 0 Ω | 47 k $\Omega$ pull-down, parallel to R2: termination 220 $\Omega$ 220 pF |

| TDO    | 0 Ω | 100 kΩ pull-down                                                         |

| Signal | R1   | R2              |

|--------|------|-----------------|

| DBGACK | 1 kΩ | 47 kΩ pull-down |

| RESET- | 0Ω   | 47 kΩ pull-up   |

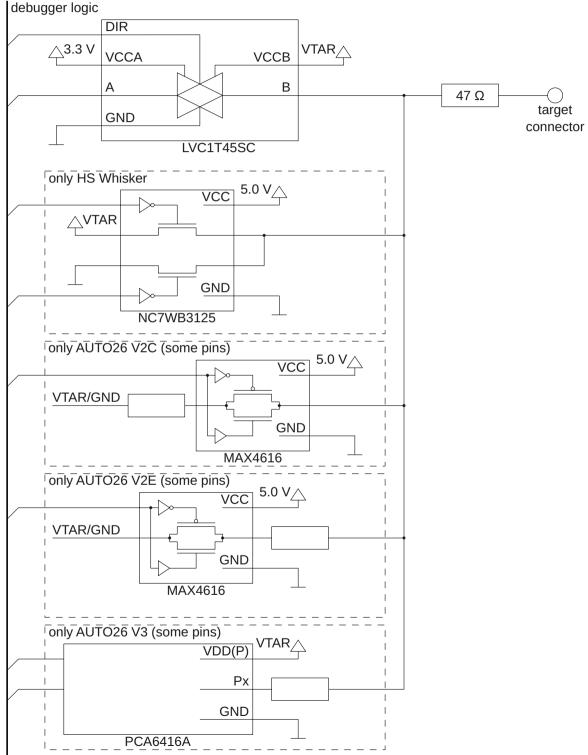

This chapter describes the actual driver/receiver circuit for debug signals inside the MIPI20T-HS Whisker and AUTO26 Debug Cable V2 and V3. For additional information, refer to the 74LVC1T45, NC7WB3125, MAX4616 and PCA6416A, data sheets. For the AUTO26 Debug Cable, all even-numbered pins are considered debug signals. For the HS whisker, even pins 2 to 10 are considered debug signals.

Each signal uses a separate bidirectional level shifter. For the AUTO26 Debug Cable V2, two such level shifters are wired in parallel to the TCK signal, with one of them being only used as an input to provide a cable-internal return clock signal.

# Dedicated Output Circuitry (only HS Whisker)

The MIPI20T-HS Whisker has bus switches wired in parallel to the input/output circuitry described above. At nominal debug VREF voltages up to 3.3 V, these are used for driving signals to the target instead of the level shifters.

# Switchable Pull Resistors (only AUTO26 V2C)

Some pins have switchable pull resistors, implemented using a MAX4616 bus switch. The following table shows which pins have resistors and whether they are configured as pull-ups or pull-downs. The "always enabled" resistors are connected directly without a bus switch.

| Pin | Signal     | R            | Direction            |

|-----|------------|--------------|----------------------|

| 1   | VREF-DEBUG | 10 kΩ        | down, always enabled |

| 2   | TMS        | <b>10</b> kΩ | down                 |

| 4   | тск        | 10 kΩ        | down                 |

| 6   | TDO        | 10 kΩ        | down                 |

| 8   | TDI        | 10 kΩ        | down                 |

| 10  | RESET-     | <b>10</b> kΩ | up                   |

| 18  | DBGRQ      | <b>10</b> kΩ | ир                   |

| 20  | DBGACK     | 10 kΩ        | up                   |

| 24  | BGRNT-     | 10 kΩ        | up, always enabled   |

Some pins have switchable pull resistors, implemented using a MAX4616 bus switch. The following table shows which pins have resistors and whether they are configured as pull-ups or pull-downs. The "always enabled" resistors are connected directly without a bus switch.

| Pin | Signal     | R     | Direction            |

|-----|------------|-------|----------------------|

| 1   | VREF-DEBUG | 10 kΩ | down, always enabled |

| 2   | TMS        | 10 kΩ | down                 |

| 4   | тск        | 10 kΩ | down                 |

| 6   | TDO        | 10 kΩ | down                 |

| 8   | TDI        | 10 kΩ | down                 |

| 10  | RESET-     | 10 kΩ | ир                   |

| 12  | RTCK       | 10 kΩ | up                   |

| 18  | DBGRQ      | 10 kΩ | up                   |

| 20  | DBGACK     | 10 kΩ | ир                   |

| 24  | BGRNT-     | 10 kΩ | up, always enabled   |

# Switchable Pull Resistors (only AUTO26 V3)

Some pins have switchable pull resistors, implemented using a common PCA6416A port expander. The port I/O supply of the expander is supplied by a buffered version of VREF. The following table shows which pins have resistors. The "always enabled" resistors are connected directly without using the port expander.

| Pin | Signal | R     | Direction            |  |

|-----|--------|-------|----------------------|--|

| 1   | VREF   | 10 kΩ | down, always enabled |  |

| 2   | TMS    | 10 kΩ | up/down              |  |

| 4   | тск    | 10 kΩ | up/down              |  |

| 6   | TDO    | 10 kΩ | up/down              |  |

| 8   | TDI    | 10 kΩ | up/down              |  |

| 10  | RESET- | 10 kΩ | up/down              |  |

| 12  | RTCK   | 10 kΩ | up/down              |  |

| Pin | Signal | R     | Direction          |  |

|-----|--------|-------|--------------------|--|

| 18  | DBGRQ  | 10 kΩ | up/down            |  |

| 20  | DBGACK | 10 kΩ | up/down            |  |

| 24  | BGRNT- | 10 kΩ | up, always enabled |  |

# **AC Electrical Characteristics**

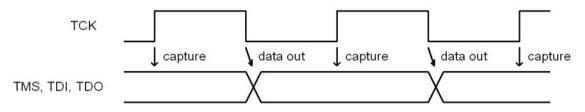

It is important for JTAG/cJTAG timing that the data on TDI and TMS is sampled on the rising edge of TCK (output on the falling edge) and that TDO changes on the falling edge of TCK. Other debug protocols have their own requirements.

All delays will affect the maximum possible JTAG frequency (TCK) which is selectable in the LAUTERBACH tool (default setting: 10 MHz). Problems with minimum setup and hold times can always be solved by simply decreasing the TCK frequency, since this increases the separation between the signal change and the sampling. Nevertheless you should keep the delays as low as possible to achieve good performance, e.g. when downloading the application program through the debugger.

The following table should give you an example for the JTAG timing considerations in case you want to work with a 20 MHz JTAG clock frequency, which results in a very good performance. Timing is measured at the connector of the probe operating in JTAG mode. Setup times and hold times are measured with respect to 50% signal level value, rise and fall times are measured at 20% and 80%. The measured values are for reference only and are not guaranteed by LAUTERBACH.

| Symbol    | Description                            | Min. | Max. | Unit |

|-----------|----------------------------------------|------|------|------|

| Ttck_high | TCK high time                          | 22   | 28   | ns   |

| Ttck_low  | TCK low time                           | 22   | 28   | ns   |

| Tsetup    | TDI, TMS setup time before rising TCK  | 21   |      | ns   |

| Thold     | TDI, TMS hold time after rising TCK    | 21   |      | ns   |

| Ttdo_out  | TDO output delay time from falling TCK | 0    | 16   | ns   |

| Ttrst_low | TRST- low time                         | 1    |      | ms   |

| Symbol    | Description                                                             | Min. | Max.        | Unit |

|-----------|-------------------------------------------------------------------------|------|-------------|------|

| Tsrst_low | RESET- low time                                                         | 1    |             | ms   |

| Trf       | output rise / fall time<br>load = 10 pF<br>load = 22 pF<br>load = 33 pF |      | 6<br>7<br>8 | ns   |

Values in table are for 20 MHz JTAG clock (TCK).

# JTAG Timing

This document uses a simplified presentation of the timings (for example any kind of jitter and skew is ignored). This is reasonable because all timings depend on a configurable JTAG TCK clock frequency; to increase the margin to cover skew, jitter etc, simply use a lower JTAG TCK clock frequency.

For JTAG ports, the debugger sends three signals to the target chip for communication via JTAG:

- **TCK**: Clock signal, driven by the debugger.

- **TMS**: Signal driven by the debugger to control the JTAG TAP controller.

- **TDI**: Signal driven by the debugger to send data into the target chip.

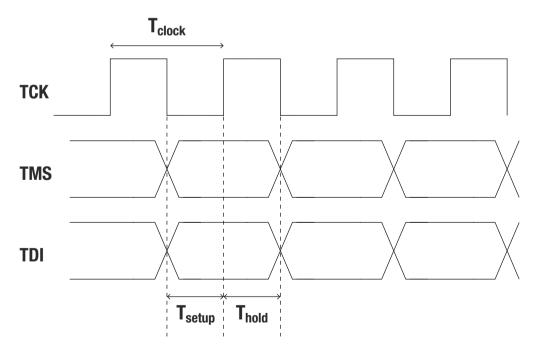

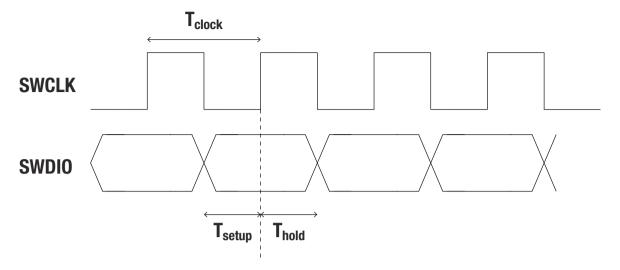

The debugger changes the value of the **TMS** and **TDI** signals coincident to the falling edge of **TCK**. So the **TMS** and **TDI** signals have the following timing relative to **TCK**:

The target chip should sample the TMS and TDI signal on the rising edge of TCK.

For the target chip this means that the debugger will produce a setup  $(T_{setup})$  and hold time  $(T_{hold})$  of half the cycle time  $(T_{clock})$  of TCK.

Example: At a TCK frequency of 1Mhz (T<sub>clock</sub> = 1us), T<sub>setup</sub> = 500ns and T<sub>hold</sub> = 500ns.

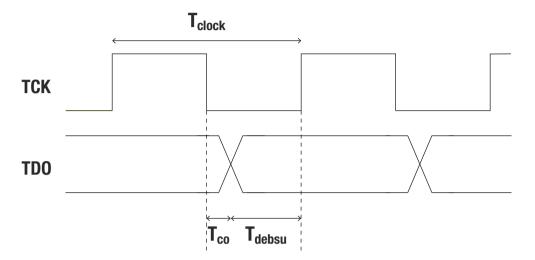

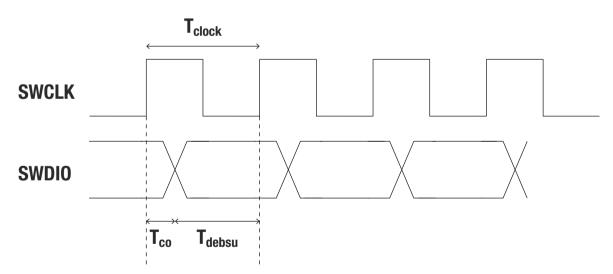

The target chip drives the **TDO** signal. The value of the **TDO** signal should change after the falling edge of **TCK**. The target chip has an implementation dependent clock to output timing ( $T_{co}$ ). The debugger per default samples the **TDO** signal on the rising edge of **TCK**:

For the debugger this means the target chip will generate data on the **TDO** signal with a setup time of  $T_{debsu} = T_{clock}/2 - T_{co}$ . The hold time of the data will be  $T_{co} + T_{clock}/2$ .

**Example**: At a **TCK** frequency of 1MHZ ( $T_{clock} = 1$ us) and  $T_{co} = 10$ ns,  $T_{debsu} = 490$ ns.

The debugger has the requirement that  $T_{co} + T_{clock}/2 > 0$ ns (hold time requirement) and  $T_{debsu} > 7.5$ ns (setup time requirement).

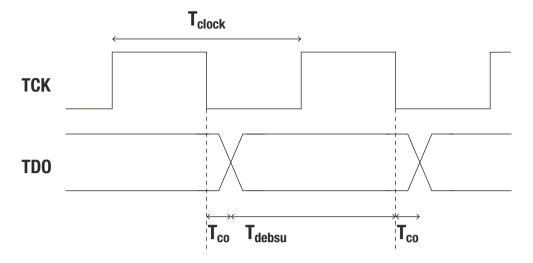

To achieve higher **TCK** frequencies (which means lower  $T_{clock}$  values), the debugger offers the option to sample the **TDO** signal on the falling edge of **TCK**. In this case the following figure explains the timing:

So in this case the target generates a setup time for the debugger of  $T_{debsu} = T_{clock} - T_{co}$ . The debugger still has a 0 ns hold time requirement, so in this case it must hold that  $T_{co} > 0$  ns.

# **SWD** Timing

This document uses a simplified presentation of the timings (for example any kind of jitter and skew is ignored). This is reasonable because all timings depend on a configurable debug clock frequency; to increase the margin to cover skew, jitter etc, simply use a lower debug clock frequency.

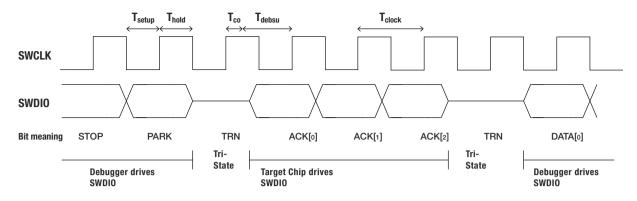

In Serial Wire Debug mode, only two signals are used to communicate with a target chip:

- **SWCLK**: Clock signal, driven by the debugger.

- **SWDIO**: Bidirectional data signal driven by both the debugger and the target chip.

When the debugger drives the SWDIO line, the debugger changes the value of SWDIO incident to the falling edge of SWCLK.