# RISC-V Debugger and Trace

# **MANUAL**

# **RISC-V Debugger and Trace**

### **TRACE32 Online Help**

**TRACE32 Directory**

**TRACE32 Index**

| TRACE32 Documents                                                  |    |

|--------------------------------------------------------------------|----|

| ICD In-Circuit Debugger                                            |    |

| Processor Architecture Manuals                                     |    |

| RISC-V                                                             |    |

| RISC-V Debugger and Trace                                          | 1  |

| History                                                            | 6  |

| Introduction                                                       | 7  |

| Brief Overview of Documents for New Users                          | 7  |

| Demo and Start-up Script                                           | 8  |

| List of Abbreviations and Definitions                              | 9  |

|                                                                    |    |

| Warning                                                            | 10 |

| Quick Start of the JTAG Debugger                                   | 11 |

| Quick Start for Debug Module Configuration                         | 16 |

| Debug Module Access via JTAG-DTM                                   | 17 |

| Implicit JTAG-DTM + DM Configuration                               | 18 |

| Explicit JTAG-DTM + DM Configuration via RVDMIAP + COREDEBUG       | 19 |

| Debug Module Access via Arm CoreSight Debug Bus                    | 21 |

| Quick Start for Multicore Debugging                                | 23 |

| SMP Debugging                                                      | 23 |

| SMP Debugging - Selective                                          | 24 |

| SMP Debugging - Multiple Debug Modules                             | 25 |

| Homogeneous SMP/AMP Debugging                                      | 26 |

| Heterogeneous SMP/AMP Debugging                                    | 27 |

| Troubleshooting                                                    | 28 |

| Communication Between Debugger and Processor Cannot Be Established | 28 |

| RISC-V Debugging                                                   | 30 |

| Debug Specification for External Debug Support                     | 30 |

| Disassembler Configuration                                         | 30 |

| Access Classes                                                     | 32 |

| Description of the Individual Access Classes                       | 32 |

| Combination of Several Access Classes                              | 34 |

| How to Create Valid Access Class Combinations                      | 36 |

|                                                                    |    |

| Breakpoints                                                        |                                       | 38 |

|--------------------------------------------------------------------|---------------------------------------|----|

| Software Breakpoints                                               |                                       | 38 |

| On-chip Breakpoint Resources                                       |                                       | 38 |

| On-chip Breakpoints for Instruction Address                        |                                       | 38 |

| On-chip Breakpoints for Data Address                               |                                       | 38 |

| On-chip Data Value Breakpoints                                     |                                       | 39 |

| Examples for Standard Breakpoints                                  |                                       | 40 |

| Floating-Point Extensions                                          |                                       | 41 |

| Hardware Performance Monitor                                       |                                       | 43 |

| Hart State: Unavailable                                            |                                       | 44 |

| Semihosting                                                        |                                       | 45 |

| Vector Extension                                                   |                                       | 46 |

| RISC-V Tracing                                                     |                                       | 47 |

| RISC-V Trace Standards                                             |                                       | 47 |

| RISC-V Trace Specifications                                        |                                       | 47 |

| RISC-V Trace IP Blocks                                             |                                       | 48 |

| N-Trace                                                            |                                       | 49 |

| E-Trace                                                            |                                       | 49 |

| Quick Start for Trace Configuration Basics                         |                                       | 50 |

| Quick Start for Trace Configuration Examples                       |                                       | 52 |

| Example A: Single-core N-Trace to On-chip Tra                      |                                       | 52 |

| Example B: Multi-core N-Trace to Off-chip Trace                    | e Sink                                | 53 |

| N-Trace                                                            |                                       | 54 |

| Trace Message Types                                                |                                       | 54 |

| Trace Trigger and Filter                                           |                                       | 54 |

| E-Trace                                                            |                                       | 54 |

| Trace Message Types                                                |                                       | 54 |

| Trace Trigger and Filter                                           |                                       | 54 |

| Command Reference: SYStem Commands                                 |                                       | 55 |

| SYStem.CONFIG.state                                                | Display target configuration          | 55 |

| _                                                                  | debugger according to target topology | 56 |

| <pre><parameters> Describing the "DebugPort"</parameters></pre>    |                                       | 59 |

| <parameters> Describing the "JTAG" Scan Cha</parameters>           |                                       | 62 |

| <parameters> Configuring an Arm CoreSight December 2.</parameters> | _                                     | 67 |

| <parameters> Configuring a RISC-V Debug Acceptable</parameters>    |                                       | 74 |

| <parameters> Describing Debug and Trace "Co</parameters>           | •                                     | 76 |

| <parameters> Describing Tessent Embedded A</parameters>            | nalytics Details                      | 77 |

| SYStem.CONFIG.HART.INDEX                                           | Set hart index                        | 78 |

| SYStem.CONFIG.NEXUS. <sub_cmd></sub_cmd>                           | Configure N-Trace trace encoder       | 79 |

| SYStem.CONFIG.RVATBBRIDGE. <sub_cmd></sub_cmd>                     | Configure RISC-V ATB bridge           | 80 |

| SYStem.CONFIG.RVFUNNEL. <sub_cmd></sub_cmd>                        | Configure RISC-V trace funnel         | 81 |

| SYStem.CONFIG.RVPIB. <sub_cmd></sub_cmd>                           | Configure RISC-V pin interface block  | 83 |

| SYStem CONFIG BYSMEMTRACE - sub_cmd>                               | RISC-V system memory sink             | 84 |

©1989-2024 Lauterbach

| SYStem.CONFIG.RVSRAMTRACE. <sub_< th=""><th>_cmd&gt; RISC-V SRAM trace sink</th><th>85</th></sub_<> | _cmd> RISC-V SRAM trace sink                  | 85  |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|

| SYStem.CPU                                                                                          | Select the CPU to be debugged                 | 86  |

| SYStem.JtagClock                                                                                    | Define JTAG frequency                         | 87  |

| SYStem.LOCK                                                                                         | Tristate the JTAG port                        | 88  |

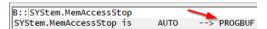

| SYStem.MemAccess                                                                                    | Select run-time memory access method          | 89  |

| SYStem.MemAccessStop                                                                                | Memory access while stopped                   | 91  |

| SYStem.Mode                                                                                         | Establish the communication with the target   | 92  |

| SYStem.state                                                                                        | Display SYStem.state window                   | 93  |

| Command Reference: SYStem Option Co                                                                 | mmands                                        | 94  |

| SYStem.Option.Address32                                                                             | Define address format display                 | 94  |

| SYStem.Option.AHBHPROT                                                                              | Select AHB-AP HPROT bits                      | 94  |

| SYStem.Option.AXIACEEnable                                                                          | ACE enable flag of the AXI-AP                 | 94  |

| SYStem.Option.AXICACHEFLAGS                                                                         | Configure AXI-AP cache bits                   | 95  |

| SYStem.Option.AXIHPROT                                                                              | Select AXI-AP HPROT bits                      | 96  |

| SYStem.Option.DAPDBGPWRUPREQ                                                                        | Force debug power in DAP                      | 97  |

| SYStem.Option.DAPNOIRCHECK                                                                          | No DAP instruction register check             | 97  |

| SYStem.Option.DAPREMAP                                                                              | Rearrange DAP memory map                      | 98  |

| SYStem.Option.DAPSYSPWRUPREQ                                                                        | Force system power in DAP                     | 98  |

| SYStem.Option.DEBUGPORTOptions                                                                      | Options for debug port handling               | 99  |

| SYStem.Option.DMACTiveRESet                                                                         | Allow debugger to reset DM via dmactive       | 100 |

| SYStem.Option.EnReset                                                                               | Allow the debugger to drive nRESET (nSRST)    | 100 |

| SYStem.Option.HARVARD                                                                               | Use Harvard memory model                      | 101 |

| SYStem.Option.HoldReset                                                                             | Set reset duration time                       | 101 |

| SYStem.Option.IMASKASM                                                                              | Disable interrupts while single stepping      | 102 |

| SYStem.Option.IMASKHLL                                                                              | Disable interrupts while HLL single stepping  | 102 |

| SYStem.Option.IrWidthDETECTION                                                                      | Disable JTAG IR width detection               | 102 |

| SYStem.Option.IsaEXTension                                                                          | Manually configure support for ISA extensions | 103 |

| SYStem.Option.KeepAlive                                                                             | Keep hart available for debugger              | 103 |

| SYStem.Option.MMUSPACES                                                                             | Separate address spaces by space IDs          | 104 |

| SYStem.Option.ResetDetection                                                                        | Choose method to detect a target reset        | 105 |

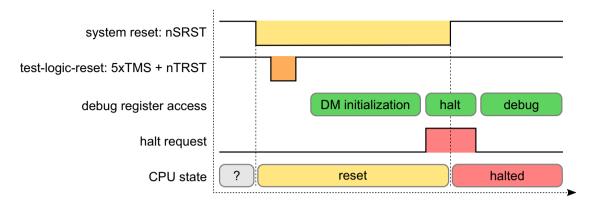

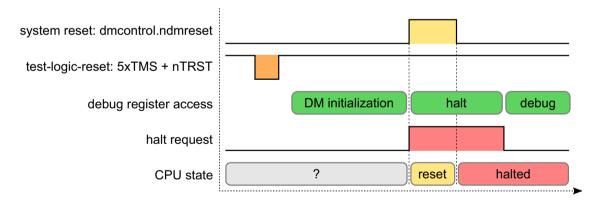

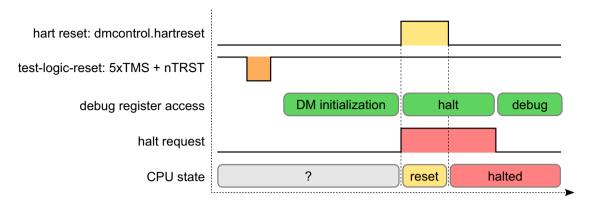

| SYStem.Option.ResetMode                                                                             | Select reset method                           | 105 |

| SYStem.Option.SOFTLONG                                                                              | Use 32-bit access to set SW breakpoints       | 108 |

| SYStem.Option.SYSDownACTion                                                                         | Define action during SYStem.Down              | 109 |

| SYStem.Option.TRST                                                                                  | Allow debugger to drive TRST                  | 109 |

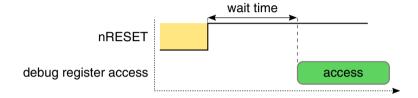

| SYStem.Option.WaitReset                                                                             | Set reset wait time                           | 110 |

| SYStem.Option.ZoneSPACES                                                                            | Enable symbol management for zones            | 111 |

| Command Reference: MMU Commands                                                                     |                                               | 113 |

| MMU.DUMP                                                                                            | Page wise display of MMU translation table    | 113 |

| MMU.List                                                                                            | Compact display of MMU translation table      | 115 |

| MMU.SCAN                                                                                            | Load MMU table from CPU                       | 117 |

| Command Reference: TrOnchip Commands                                                                |                                               |     |

| Command Reference: BVATBBBIDGE Co                                                                   | mmande                                        | 120 |

©1989-2024 Lauterbach

| RVATBBRIDGE. <sub_cmd></sub_cmd>    | Control RISC-V trace ATB bridge                    | 120 |  |

|-------------------------------------|----------------------------------------------------|-----|--|

| Command Reference: RVPIB Com        | mands                                              | 121 |  |

| RVPIB. <sub_cmd></sub_cmd>          | Control RISC-V pin interface block                 | 121 |  |

| Command Reference: ETRACE (E-Trace) |                                                    |     |  |

| RVETRACE.ON                         | Enable E-TRACE                                     | 123 |  |

| Command Reference: NEXUS (N-T       | race)                                              | 124 |  |

| NEXUS.ON                            | Power on N-Trace encoder                           | 124 |  |

| NEXUS.OFF                           | Power off N-Trace encoder                          | 124 |  |

| NEXUS.TimeStamps                    | Enable / disable N-Trace encoder timestamps        | 124 |  |

| NEXUS.TraceID                       | Configure trace source ID of N-Trace encoder       | 125 |  |

| NEXUS.TraceIDWidth                  | Configure trace source ID width of N-Trace encoder | 125 |  |

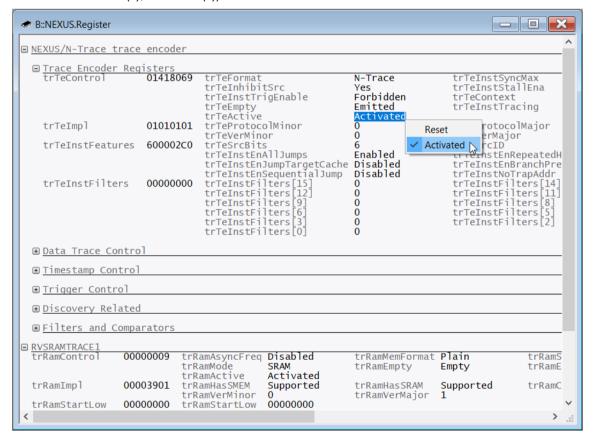

| NEXUS.Register                      | Show trace control registers                       | 126 |  |

| NEXUS.RESet                         | Reset N-Trace encoder                              | 127 |  |

| Target Adaption                     |                                                    | 128 |  |

| Connector Type and Pinout           |                                                    | 128 |  |

| BISC-V Debug Cable with 20 pin      | Connector                                          | 128 |  |

# **RISC-V Debugger and Trace**

### Version 18-Dec-2024

## **History**

| 12-Dec-2024 | Chapter 'RISC-V Tracing' added. A set of commands for configuring the trace infrastructure has been introduced.                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Aug-2024 | New command SYStem.Option.IrWidthDETECTION.                                                                                                                                 |

| 02-Aug-2024 | MMU.DUMP, MMU.List, and MMU.SCAN commands updated: 'CPU specific Tables' descriptions added.                                                                                |

| 24-Jul-2024 | New AccessPort RISC-V parameters for the SYStem.CONFIG command. A detailed description can be found in ' <parameters> Configuring a RISC-V Debug Access Port'.</parameters> |

| 22-Jul-2024 | New subchapter 'SMP Debugging - Multiple Debug Modules'.                                                                                                                    |

| 17-Nov-2023 | New command SYStem.Option.IsaEXTension.                                                                                                                                     |

| 18-Aug-2023 | Marked <b>SYStem.CONFIG.HARTINDEX</b> as deprecated command and replaced by SYStem.CONFIG.HART.INDEX.                                                                       |

| 17-Oct-2022 | New subchapter 'Vector Extension'.                                                                                                                                          |

| 06-Oct-2022 | New command SYStem.Mode.StandBy.                                                                                                                                            |

| 06-Oct-2022 | New subchapter: 'Hart State: Unavailable'.                                                                                                                                  |

| 29-Aug-2022 | New command: SYStem.Option.DMACTiveRESet.                                                                                                                                   |

| 20-Jul-2022 | For the MMU.SCAN ALL command, CLEAR is now possible as an optional second parameter.                                                                                        |

| 02-Mar-2022 | New command: SYStem.Option.KeepAlive.                                                                                                                                       |

| 04-Sep-2017 | Initial version.                                                                                                                                                            |

### Introduction

This manual serves as a guideline for debugging and tracing one or multiple RISC-V cores via TRACE32.

Please note that only the **Processor Architecture Manual** (the document you are currently reading) is specific to the core architecture. All other parts of the online help are general and independent of any core architecture. Therefore, if you have questions related to the core architecture, the **Processor Architecture Manual** should be your primary reference.

### **Brief Overview of Documents for New Users**

#### **Architecture-independent information:**

- "Debugger Tutorial" (debugger\_tutorial.pdf): Get familiar with the basic features of a TRACE32 debugger.

- "General Commands" (general ref <x>.pdf): Alphabetic list of debug commands.

- "OS Awareness Manuals" (rtos\_<os>.pdf): TRACE32 PowerView can be extended for operating system-aware debugging. The appropriate OS Awareness manual informs you how to enable the OS-aware debugging.

### **Architecture-specific information:**

- "Processor Architecture Manuals": These manuals describe commands that are specific for the

processor architecture supported by your Debug Cable. To access the manual for your processor

architecture, proceed as follows:

- Choose **Help** menu > **Processor Architecture Manual**.

#### **PRACTICE Script Language:**

- "Training Script Language PRACTICE" (training practice.pdf)

- "PRACTICE Script Language Reference Guide" (practice\_ref.pdf)

#### Video Tutorials:

Lauterbach YouTube channel

To get started with the most important manuals, use the **Welcome to TRACE32!** dialog (**WELCOME.view**):

### **Demo and Start-up Script**

Lauterbach provides ready-to-run start-up scripts for known hardware that is based on RISC-V.

### To search for PRACTICE scripts, do one of the following in TRACE32 PowerView:

- Type at the command line: WELCOME.SCRIPTS

- or choose File menu > Search for Script.

You can now search the demo folder and its subdirectories for PRACTICE start-up scripts (\*.cmm) and other demo software.

You can also manually navigate in the ~~/demo/riscv/ subfolder of the system directory of TRACE32.

### **List of Abbreviations and Definitions**

| CSR                     | Control and Status Register                                          |

|-------------------------|----------------------------------------------------------------------|

| DM                      | Debug Module, as defined by the RISC-V debug specification           |

| DTM                     | Debug Transport Module, as defined by the RISC-V debug specification |

| HART<br>Hardware thread | Single RISC-V core contains one or multiple hardware threads         |

| XLEN                    | Current width of a RISC-V general purpose register in bits           |

### WARNING:

To prevent debugger and target from damage it is recommended to connect or disconnect the Debug Cable only while the target power is OFF.

#### Recommendation for the software start:

- 1. Disconnect the Debug Cable from the target while the target power is off.

- 2. Connect the host system, the TRACE32 hardware and the Debug Cable.

- 3. Power ON the TRACE32 hardware.

- 4. Start the TRACE32 software to load the debugger firmware.

- 5. Connect the Debug Cable to the target.

- 6. Switch the target power ON.

- 7. Configure your debugger e.g. via a start-up script.

### Power down:

- 1. Switch off the target power.

- 2. Disconnect the Debug Cable from the target.

- 3. Close the TRACE32 software.

- 4. Power OFF the TRACE32 hardware.

### Quick Start of the JTAG Debugger

Starting up the debugger is done as follows:

#### 1. Reset all debugger settings.

**RESet**

The **RESet** command ensures that no debugger settings persist from a previous debug session; all settings are restored to their default values. Using RESet is unnecessary if you begin the debug session immediately after launching TRACE32 PowerView. Note that RESet does not reset the target.

#### 2. Select the chip or core you intend to debug.

SYStem.CPU <cpu type>

Select a core only if you are debugging a confidential chip or a chip not yet supported by TRACE32. For chips already supported by TRACE32, the debugger automatically configures the SYStem.CONFIG and SYStem.Option commands for optimal compatibility, often requiring no additional setup. However, please note that the default configuration may not always be ideal for your specific target hardware.

#### 3. Configure the JTAG interface.

The default clock frequency is 10 MHz. You can manually set the JTAG clock frequency used by the debugger to communicate with the target hardware by using the SYStem. JtaqClock command. The maximum clock frequency may vary depending on your FPGA design configuration

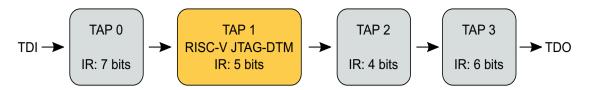

In case of a JTAG daisy chain use command SYStem.DETECT SHOWChain to scan the chain. The result is shown in a window. Double-click on the desired core to tell the debugger which core you'd like to debug.

### 3.A) Systems with RISC-V JTAG-DTM

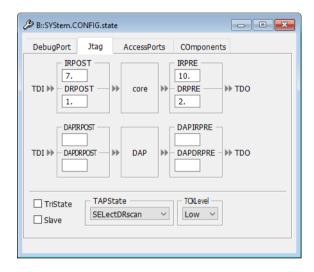

If the RISC-V Debug Module (DM) is accessible via a RISC-V JTAG-DTM, and the JTAG TAP of that JTAG-DTM is daisy-chained with other TAPs, then you can manually configure the JTAG daisy chain in one of two ways:

- For simple systems use implicit JTAG-DTM configuration via SYStem.CONFIG.IRPOST, SYStem.CONFIG.IRPRE, SYStem.CONFIG.DRPOST and SYStem.CONFIG.DRPRE.

- For more complex systems use explicit JTAG-DTM configuration via SYStem.CONFIG.RVDMIAP

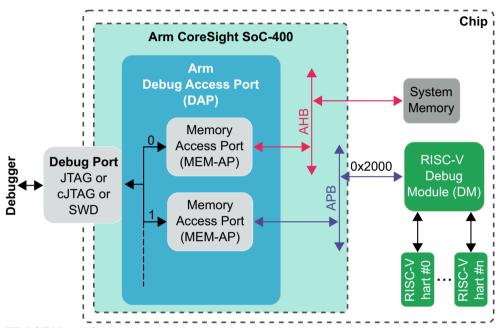

#### 3.B) Systems with Arm CoreSight DAP

If the target system has an Arm CoreSight Debug Access Port (Arm DAP), and the JTAG TAP of the DAP is daisy-chained with other TAPs, then you can manually configure the JTAG daisy chain with SYStem.CONFIG.DAPIRPOST, SYStem.CONFIG.DAPIRPRE, SYStem.CONFIG.DAPDRPOST and SYStem.CONFIG.DAPDRPRE.

#### 4. Configure memory access ports (if available).

#### 4.1) Systems with RISC-V JTAG-DTM (DMI Access Port)

If the target system does have one or more RISC-V JTAG-DTMs, and if the Debug Module Interface (DMI) debug bus behind these JTAG-DTMs needs to be accessible to the user via the 'DMI' access

class, then DMI access ports need to be configured. See explicit JTAG-DTM configuration via SYStem.CONFIG.RVDMIAP for details.

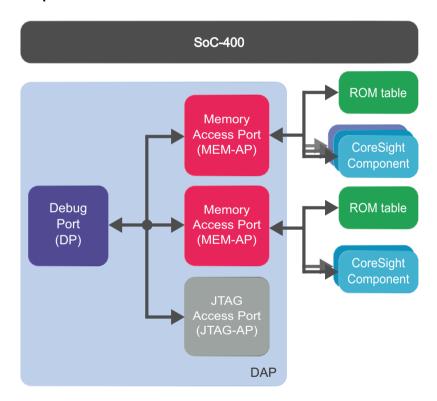

### 4.2) Systems with Arm CoreSight memory access ports

If the target SoC has an Arm CoreSight debug infrastructure, then the memory access ports need to be configured in order to make their buses accessible via the respective access classes.

For Arm SoC-400, see SYStem.CONFIG.APBAP.Port, SYStem.CONFIG.AHBAP.Port and SYStem.CONFIG.AXIAP.Port for details.

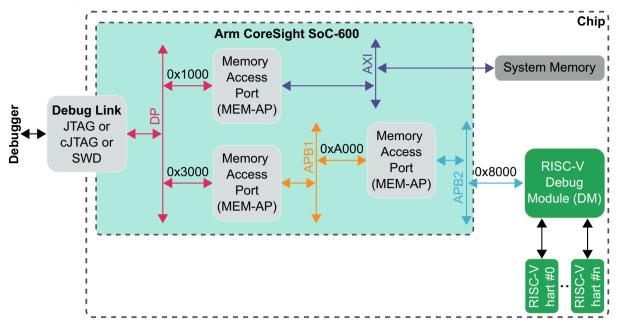

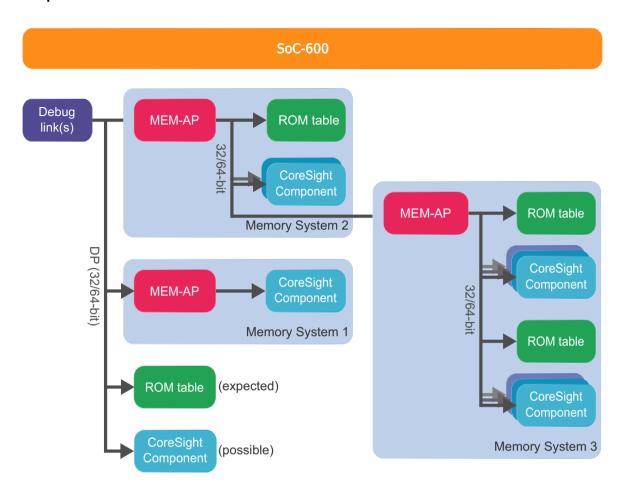

For Arm SoC-600, see SYStem.CONFIG.APBAP.Base, SYStem.CONFIG.AHBAP.Base and SYStem.CONFIG.AXIAP.Base for details.

5. Tell the debugger how to access the RISC-V Debug Module.

See chapter "Quick Start for Debug Module Configuration" (debugger riscv.pdf) for details.

6. Select the reset method.

```

SYStem.Option.ResetMode <method>

```

If the debugger is supposed to perform a system reset or core reset while connecting to the target. then the reset method that is most suitable for the target needs to be configured with SYStem.Option.ResetMode.

7. Connect to target.

```

SYStem.Up

```

This command establishes the JTAG communication to the target. It resets the processor and enters debug mode (halts the processor; ideally at the reset vector). After this command is executed, it is possible to access memory and registers.

Some devices can not communicate via JTAG while in reset or you might want to connect to a running program without causing a target reset. In this case use

```

SYStem.Mode Attach

```

instead. A Break.direct will halt the processor.

8. Load the program you want to debug.

```

Data.LOAD <file>

```

This loads the executable to the target and the debug/symbol information to the debugger's host. If the program is already on the target and you just need the debug/symbol information then load with /NoCODE option.

A detailed description of the Data.LOAD command and all available options is given in the "General **Commands Reference**".

LAUTERBACH recommends to prepare a PRACTICE script (\*.cmm, ASCII file format) to be able to do all the necessary actions with only one command, such as the command DO <file>.

The following example shows a system configuration for a RISC-V system with JTAG-DTM:

```

RESet.

; Reset the debugger configuration

SYStem.CPU FU540-C000

; Select the SoC/CPU/core

SYStem.JtagClock 5.MHz

; Set JTAG clock frequency

SYStem.CONFIG IRPRE 4.

; Configure JTAG daisy chain

SYStem.CONFIG IRPOST 0.

SYStem.CONFIG DRPRE 1.

SYStem.CONFIG DRPOST 0.

SYStem.Option.ResetMode NDMRST

: Select the reset method

```

A typical example for a start sequence (in addition to the above configuration) might look like the following:

```

; Reset the target, stop the core at

SYStem.Up

; the reset vector, enter debug mode

Data.LOAD.Elf riscv_le.elf

; Load the application

; Set the PC to function main

Register.Set PC main

Register.Set X2 0x63FFFFFC

; Set the stack pointer to

: address 0x63FFFFFC

Break.Set P:0x1000 /Program

; Set breakpoint to address P:0x1000

List.Mix

; Open source code window

Register.view /SpotLight

; Open register window

Frame.view /Locals /Caller

; Open the stack frame with

: local variables

Var.Watch %SpotLight var1 var2

: Open watch window for variables

PER.view

; Open window for tree view of

; system peripherals

```

For more details about the configuration of a RISC-V system with JTAG-DTM, please see chapter Debug Module access via JTAG-DTM.

LAUTERBACH recommends to prepare a PRACTICE script (\*.cmm, ASCII file format) to be able to do all the necessary actions with only one command, such as the command **DO** *<file>*.

The following example shows a configuration for a RISC-V core in an Arm CoreSight SoC-400 system:

```

; Reset debugger configuration

RESet.

: Select the SoC/CPU/core

SYStem.CPU RV32

SYStem.JtagClock 5.MHz

; Set JTAG clock frequency

SYStem.CONFIG.DAPIRPRE

; Configure JTAG daisy chain

SYStem.CONFIG.DAPIRPOST 0.

SYStem.CONFIG.DAPDRPRE

SYStem.CONFIG.DAPDRPOST 0.

SYStem.Option.ResetMode NDMRST

; Select the reset method

SYStem.CONFIG.APBAP1.Port 4.

; Configure DAP memory

SYStem.CONFIG.AXIAP1.Port 5.

; access ports (SoC-400)

SYStem.CONFIG.COREDEBUG.Base APB:0x2000

; Configure APB base address

; of RISC-V debug module

; Reset the target, stop the

SYStem.Up

; core at the reset vector and

; enter debug mode

```

For additional configuration examples of a RISC-V system integrated into an Arm **CoreSight SoC-400** system, please see chapter "Debug Module Access via Debug Bus", **subchapter for SoC-400**.

LAUTERBACH recommends to prepare a PRACTICE script (\*.cmm, ASCII file format) to be able to do all the necessary actions with only one command, such as the command **DO** <*file>*.

The following example shows a configuration for a RISC-V core in an Arm CoreSight SoC-600 system:

```

; Reset debugger configuration

RESet.

: Select the SoC/CPU/core

SYStem.CPU RV32

SYStem.JtagClock 5.MHz

; Set JTAG clock frequency

SYStem.CONFIG.DAPIRPRE

; Configure JTAG daisy chain

SYStem.CONFIG.DAPIRPOST 0.

SYStem.CONFIG.DAPDRPRE

SYStem.CONFIG.DAPDRPOST 0.

SYStem.Option.ResetMode NDMRST

: Select the reset method

SYStem.CONFIG.APBAP1.Base DP:0x30000

; Configure memory access port

SYStem.CONFIG.AXIAP1.Base DP:0x70000

; base addresses (SoC-600)

SYStem.CONFIG.COREDEBUG.Base APB:0x2000

; Configure APB base address

; of RISC-V debug module

; Reset the target, stop the

SYStem.Up

; core at the reset vector and

; enter debug mode

```

For additional configuration examples of a RISC-V system integrated into an Arm **CoreSight SoC-600** system, please see chapter "Debug Module Access via Debug Bus", **subchapter for SoC-600**.

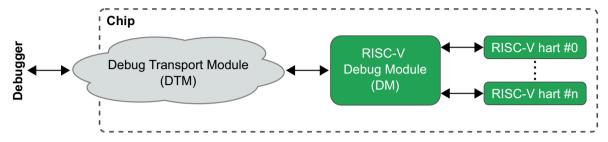

## **Quick Start for Debug Module Configuration**

The RISC-V Debug Module (DM) is the central IP block that contains the debug registers, which give the debugger access to most RISC-V debug functionalities. Usually all RISC-V hardware threads (harts) in a system are connected to the same DM.

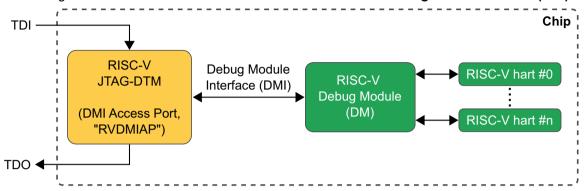

A DM can be integrated into a system in various ways. Any abstract IP block which provides access to the debug registers of the DM is called *Debug Transport Module (DTM)*:

The RISC-V debug specification does *not* specify which interface and implementation the DTM needs to have. In theory, the implementation of the DTM can be completely chip-specific. The RISC-V debug specification does however define one standardized DTM, the so-called **RISC-V JTAG-DTM**.

The debugger needs to know how the DM's debug registers can be accessed. That is why this chapter provides a quick start for DM configuration. The following examples cover the most common use cases for DM integration into a system:

- Example A: Debug Module Access via JTAG-DTM

- Example A.1: Implicit JTAG-DTM + DM Configuration

- Example A.2: Explicit JTAG-DTM + DM Configuration via RVDMIAP + COREDEBUG

- Example B: Debug Module Access via Arm CoreSight Debug Bus

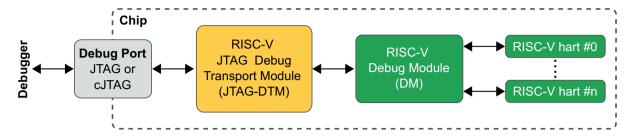

### **Debug Module Access via JTAG-DTM**

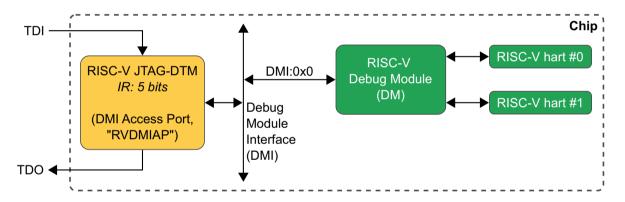

The simplest way to access a RISC-V Debug Module (DM) from an external JTAG interface is via a JTAG Debug Transport Module (JTAG-DTM). The JTAG-DTM is specified and standardized by the RISC-V debug specification. A simple example setup could look as follows:

### JTAG-DTM with JTAG port

If the JTAG-DTM does have a normal JTAG port (IEEE 1149.1), then **SYStem.CONFIG.DEBUGPORTTYPE** needs to be set to "JTAG" (default setting).

#### JTAG-DTM with cJTAG port

However, the RISC-V debugger does also support JTAG-DTMs with a *cJTAG* port (IEEE 1149.7). In this case, **SYStem.CONFIG.DEBUGPORTTYPE** needs to be set to "cJTAG".

### Implicit JTAG-DTM + DM Configuration

The RISC-V debugger considers a JTAG-DTM the *default* way to access the RISC-V Debug Module (DM). This means if no user configuration defines any other way to access the DM, then the RISC-V debugger automatically **implies** (without any user configuration):

- the existence of a single RISC-V JTAG-DTM that is connected to the external debug port

- the existence of a single RISC-V DM that is directly connected to that JTAG-DTM at base address DMI:0x0.

This implied setup is depicted in the above chapter **Debug Module Access via JTAG-DTM**. The implicit JTAG-DTM configuration does not allow access to the "DMI" access class.

If the JTAG TAP of the JTAG-DTM is daisy-chained with other TAPs, then you can manually configure the JTAG daisy chain with **SYStem.CONFIG.IRPOST**, **SYStem.CONFIG.IRPRE**, **SYStem.CONFIG.DRPOST** and **SYStem.CONFIG.DRPRE**. These commands only apply to the implicit JTAG-DTM configuration.

For more complicated hardware setups, please refer to the Explicit JTAG-DTM Configuration instead.

NOTE:

The implicit configuration mode and the explicit configuration mode of the RVDMIAP and the RISC-V DM can not be mixed. This means if at least one RVDMIAP was explicitly configured, then the RISC-V DM needs to be explicitly configured via SYStem.CONFIG.COREDEBUG.Base as well.

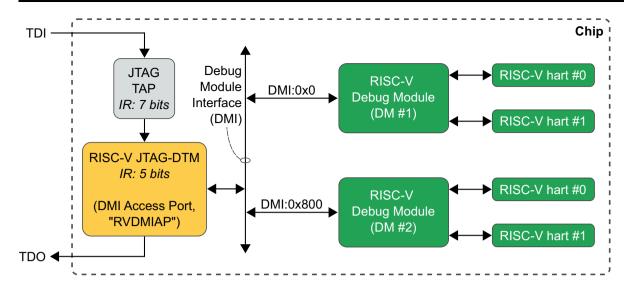

### **Explicit JTAG-DTM + DM Configuration via RVDMIAP + COREDEBUG**

The RISC-V debug specification defines the **RISC-V JTAG Debug Transport Module (JTAG-DTM)**, which is a standardized RISC-V IP block that can access the debug registers of the **RISC-V Debug Module (DM)**. The debug bus that connects the JTAG-DTM to the DM is called the **Debug Module Interface (DMI)**.

As the RISC-V JTAG-DTM provides access to the DMI bus, it can be considered a RISC-V DMI Access Port (RVDMIAP). See the chapter about the RVDMIAP for details.

The explicit configuration of the RVDMIAP and DM allows to represent more complex hardware setups, and to get access to the "DMI:" access class. The following examples show common RVDMIAP and DM configuration scenarios.

#### NOTE:

The implicit configuration mode and the explicit configuration mode of the RVDMIAP and the RISC-V DM can not be mixed. This means if at least one RVDMIAP was explicitly configured, then the RISC-V DM needs to be explicitly configured via SYStem.CONFIG.COREDEBUG.Base as well.

#### Example #1: one JTAG TAP, one DM

#### **Debugger configuration example** (for SMP debugging):

```

SYStem.CPU <cpu>

SYStem.CONFIG CORE 1. 1.

SYStem.CONFIG CoreNumber 2.

SYStem.CONFIG HART.INDEX 0. 1.

CORE.ASSIGN 1. 2.

SYStem.CONFIG RVDMIAP1.DebugSource DebugPort

; External debug port

SYStem.CONFIG RVDMIAP1.IRWIDTH 5.

; Standard JTAG-DTM IR

SYStem.CONFIG RVDMIAP1.IRPRE 0.

: No other JTAG TAPs

SYStem.CONFIG RVDMIAP1.IRPOST 0.

SYStem.CONFIG RVDMIAP1.DRPRE 0.

SYStem.CONFIG RVDMIAP1.DRPOST 0.

SYStem.CONFIG COREDEBUG.Base DMI:0x0 DMI:0x0

; RISC-V DM

```

### **Debugger configuration example** (for SMP debugging):

```

SYStem.CPU <cpu>

SYStem.CONFIG CORE 1. 1.

SYStem.CONFIG CoreNumber 4.

SYStem.CONFIG HART.INDEX 0. 1. 0. 1.

CORE.ASSIGN 1. 2. 3. 4.

SYStem.CONFIG RVDMIAP1.DebugSource DebugPort

; External debug port

SYStem.CONFIG RVDMIAP1.IRWIDTH 5.

; Standard JTAG-DTM IR

SYStem.CONFIG RVDMIAP1.IRPRE 0.

SYStem.CONFIG RVDMIAP1.IRPOST 7.

; other JTAG TAP

SYStem.CONFIG RVDMIAP1.DRPRE 0.

SYStem.CONFIG RVDMIAP1.DRPOST 1.

; other JTAG TAP

SYStem.CONFIG COREDEBUG.Base

; RISC-V DM byte offsets

DMI:0x0 DMI:0x0 DMI:0x800 DMI:0x800

```

### **Debug Module Access via Arm CoreSight Debug Bus**

An alternative way to make the RISC-V Debug Module (DM) accessible to a debugger is to map the debug registers of the DM on an existing debug bus.

If the DM debug registers are bus-mapped then the bus type (i.e. the access class) and the base address of the DM must be configured with the command **SYStem.CONFIG COREDEBUG.Base**.

### **Example: Arm CoreSight SoC-400**

The following example shows a DM that is mapped on a debug bus of an Arm CoreSight SoC-400 system:

### **TRACE32** configuration:

SYStem.CONFIG AHBAP1.Port 0.

SYStem.CONFIG APBAP1.Port 1.

SYStem.CONFIG COREDEBUG.Base APB:0x2000

The type of the debug port (JTAG, cJTAG or SWD) can be configured via **SYStem.CONFIG.DEBUGPORTTYPE.**

The following example shows a DM that is mapped on a debug bus of an Arm CoreSight SoC-600 system:

### **TRACE32** configuration:

SYStem.CONFIG AXIAP1.Base DP:0x1000

SYStem.CONFIG APBAP1.Base DP:0x3000

SYStem.CONFIG APBAP2.Base APB1:0xA000

SYStem.CONFIG COREDEBUG.Base APB2:0x8000

The type of the debug port (JTAG, cJTAG or SWD) can be configured via **SYStem.CONFIG.DEBUGPORTTYPE.**

### **Quick Start for Multicore Debugging**

This chapter provides a quick start for multicore processing. The following example scenarios cover the most common use cases for **s**ymmetric **m**ulti**p**rocessing (SMP) and **a**symmetric **m**ulti**p**rocessing (AMP):

- Example A: SMP Debugging

- Example B: SMP Debugging Selective

- Example C: SMP Debugging Multiple Debug Modules

- Example D: Homogeneous SMP/AMP Debugging

- Example E: Heterogeneous SMP/AMP Debugging

### **SMP Debugging**

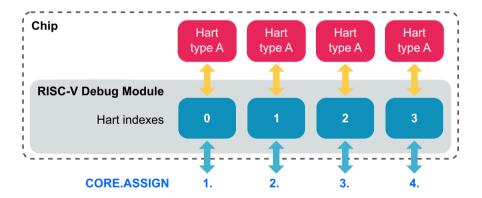

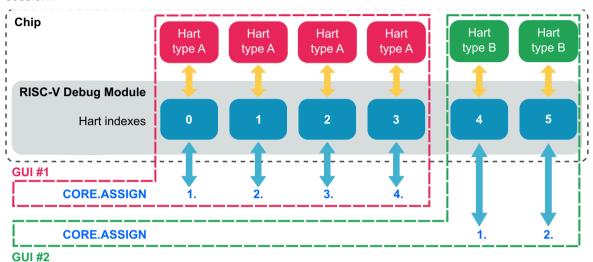

This scenario for homogeneous symmetric multiprocessing (SMP) covers the following setup:

4 hardware threads (harts) of the same type are connected to the same RISC-V Debug Module of the same chip, with the hart indexes of the RISC-V Debug Module ranging from 0 to 3. All 4 harts will be debugged simultaneously via SMP.

### Example A:

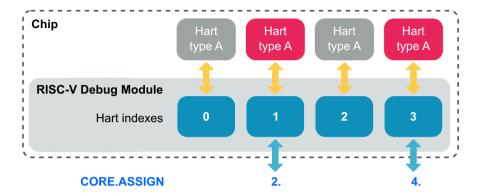

### **SMP Debugging - Selective**

This scenario for homogeneous symmetric multiprocessing (SMP) covers the following setup:

4 hardware threads (harts) of the same type are connected to the same RISC-V Debug Module of the same chip, with the hart indexes of the RISC-V Debug Module ranging from 0 to 3. The harts with hart indexes 1 and 3 will be debugged simultaneously via SMP.

### Example B:

```

SYStem.CPU <type_a_cpu>

SYStem.CONFIG CORE 1. 1. ; Core group 1 for chip 1

SYStem.CONFIG CoreNumber 4. ; 4 harts of type A in total

SYStem.CONFIG HART.INDEX 0. 1. 2. 3.

CORE.ASSIGN 2. 4. ; Assign harts with the

; logical indexes 2 and 4

```

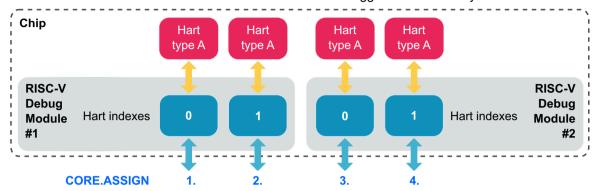

### **SMP Debugging - Multiple Debug Modules**

This scenario for homogeneous symmetric multiprocessing (SMP) covers the following setup:

4 hardware threads (harts) of the same type are connected to two RISC-V Debug Modules (DM) of the same chip. Each RISC-V DM is connected to two harts. The hart indexes of each RISC-V DM start at 0, so each DM has the hart indexes 0 and 1. All 4 harts will be debugged simultaneously via SMP.

### Example C:

```

SYStem.CPU <type_a_cpu>

SYStem.CONFIG CORE 1. 1. ; Core group 1 for chip 1

SYStem.CONFIG CoreNumber 4. ; 4 harts of type A in total

SYStem.CONFIG HART.INDEX 0. 1. 0. 1. ; DM hart index starts at 0

CORE.ASSIGN 1. 2. 3. 4. ; Assign all 4 harts to the

; SMP session

```

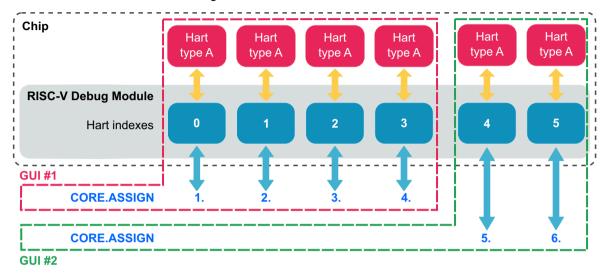

### Homogeneous SMP/AMP Debugging

This scenario covers both homogeneous symmetric multiprocessing (SMP) and asymmetric multiprocessing (AMP).

6 hardware threads (harts) of the same type are connected to the same RISC-V Debug Module of the same chip, with the hart indexes of RISC-V Debug Module ranging from 0 to 5. The first 4 harts will be debugged in an SMP session, and the remaining 2 harts in another SMP session.

### Example D:

```

; ---- TRACE32 PowerView GUI #1 ---

SYStem.CPU <type_a_cpu>

SYStem.CONFIG CORE 1. 1.

; Core group 1 for chip 1

SYStem.CONFIG CoreNumber 6.

; 6 harts of type A in total

SYStem.CONFIG HART.INDEX 0. 1. 2. 3. 4. 5.

CORE.ASSIGN 1. 2. 3. 4.

; Assign the first 4 harts

```

```

; ---- TRACE32 PowerView GUI #2 ---

SYStem.CPU <type_a_cpu>

SYStem.CONFIG CORE 2. 1.

; Core group 2 for chip 1

SYStem.CONFIG CoreNumber 6.

; 6 harts of type A in total

SYStem.CONFIG HART.INDEX 0. 1. 2. 3. 4. 5.

CORE.ASSIGN 5. 6.

; Assign the last 2 harts

```

### **Heterogeneous SMP/AMP Debugging**

This scenario covers both heterogeneous symmetric multiprocessing (SMP) and asymmetric multiprocessing (AMP).

6 hardware threads (harts) are connected to the same RISC-V Debug Module of the same chip, with the hart indexes of the RISC-V Debug Module ranging from 0 to 5. The first 4 harts are of type A and will be debugged in an SMP session, and the remaining 2 harts are of type B and will be debugged in another SMP session

# Example E:

```

; ---- TRACE32 PowerView GUI #1

SYStem.CPU <type_a_cpu>

; Core group 1 for chip 1

SYStem.CONFIG CORE 1. 1.

; 4 harts of type A in total

SYStem.CONFIG CoreNumber 4.

SYStem.CONFIG HART.INDEX 0. 1. 2. 3.

; Hart indexes of type A

CORE.ASSIGN 1. 2. 3. 4.

; Assign all 4 harts of type A

```

```

; ---- TRACE32 PowerView GUI #2

SYStem.CPU <type b cpu>

SYStem.CONFIG CORE 2. 1.

; Core group 2 for chip 1

; 2 harts of type B in total

SYStem.CONFIG CoreNumber 2.

SYStem.CONFIG HART.INDEX 4. 5.

; Hart indexes of type B

CORE.ASSIGN 1. 2.

; Assign all 2 harts of type B

```

### Communication Between Debugger and Processor Cannot Be Established

Typically SYStem.Mode Up or SYStem.Mode Attach is the first command of a debug session for which communication with the target board is required. That is why it is the most common command to fail in case that there is any issue with the user configuration, debug connection or target.

### NOTE:

In case of any error during the debug session, we highly recommend to open the **AREA.view** window. This window usually contains a list of all recent warnings and error messages, which can be very helpful for error diagnosis.

The error messages in the AREA.view window (which can be identified by their red color) usually try to give the user a short error description and a reason for the error. However in some scenarios it can be difficult to deduce the error cause from an error message, because the error message is either too generic or the error message is only the follow-up error of another issue that has nothing to do with the actual error message. In order to still be able to resolve the error in such scenarios, the following lists the most common error causes:

- The target has no power or the debug cable is not connected to the target. This results in the error message "target power fail".

- You did not select the correct core type via **SYStem.CPU** <*type*>.

- There is an issue with the JTAG interface. See www.lauterbach.com/adriscv.html and the manuals or schematic of your target to check the physical and electrical interface. Maybe there is the need to set jumpers on the target to connect the correct signals of the JTAG connector.

- Your RISC-V Debug Module (DM) is mapped on a debug bus, but the base address of the DM is either not configured or incorrect. Check the settings of SYStem.CONFIG.COREDEBUG.Base.

- You might have several TAP controllers in your JTAG-chain. Example: The TAP of the JTAG-DTM could be in a chain with other TAPs from other CPUs. In this case you have to check your preand post-bit configuration. See for example SYStem.CONFIG.IRPRE or SYStem.CONFIG.DAPIRPRE.

- The default frequency of the JTAG/SWD/cJTAG debug port is too high, especially if you emulate your core or if you use an FPGA-based target. In this case try SYStem.JtagClock 50kHz and optimize the speed when you got it working.

- The target cannot communicate with the debugger while in reset. Try SYStem. Mode Attach followed by Break.direct instead of SYStem.Mode Up.

- The target does not support the configured reset method. Select a different reset method via SYStem.Option.ResetMode.

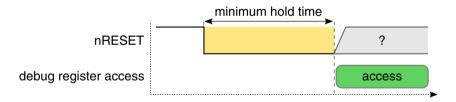

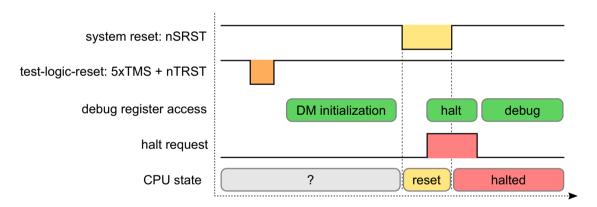

- The target needs a certain setup time during the reset assertion or after the reset release. Try to adapt the reset timing via SYStem.Option.WaitReset and/or SYStem.Option.HoldReset.

- There is a watchdog which needs to be deactivated.

- There is the need to enable (jumper) the debug features on the target. It will e.g. not work if nTRST signal is directly connected to ground on target side.

- The target is in an unrecoverable state. Re-power your target and try again.

- The core has no power or is kept in reset.

- The core has no clock.

### **Debug Specification for External Debug Support**

The Lauterbach debug driver for RISC-V is developed according to the official RISC-V debug specification for external debug support. The latest official version can be found at <a href="https://riscv.org/technical/specifications/">https://riscv.org/technical/specifications/</a>.

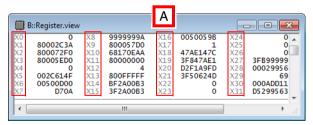

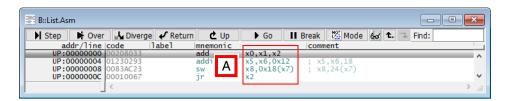

### **Disassembler Configuration**

The **SETUP.DIS** command enables you to format the disassembler display in TRACE32 windows, such as **List.auto**. The following *<constants>* command parameters are specific to RISC-V:

- AbiNames, which activates the ABI (Application Binary Interface) naming convention for generalpurpose registers.

- **RegNames** (default naming scheme), which employs the register number format (x0, x1, ..., x31) for these registers.

### Example:

SETUP.DIS AbiNames

This SETUP command displays the general-purpose registers in the **Register.view** window according to the specified naming scheme. It also ensures that the general-purpose registers are displayed using the chosen naming scheme in all TRACE32 windows that show disassembled code, such as **List.Auto**.

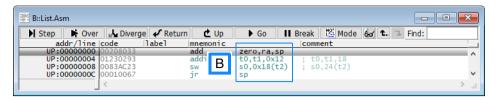

A Register number naming scheme.

**B** ABI naming scheme.

It is advisable to include the disassembler setup in the startup script.

### **Access Classes**

In TRACE32, addresses always consist of two parts:

- An access class which defines:

- What kind of memory (or register) to access

- How to perform the access

- A number that determines the address of the access

Each access class consists of one or more letters/numbers followed by a colon (:).

### Examples:

```

Data.dump D:0x100

Data.dump AXI:0x80000000--0x80000FFF

PRINT Data.Long(CSR:0x300)

```

It is possible to combine individual access classes.

For more background information, see the chapter about access classes in the TRACE32 Concepts.

#### In this section:

- Description of the Individual Access Classes

- Combination of Several Access Classes

- How to Create Valid Access Class Combinations

### **Description of the Individual Access Classes**

|   | Description                                                                                                       |

|---|-------------------------------------------------------------------------------------------------------------------|

| Р | Program memory access. See SYStem.MemAccessStop and SYStem.MemAccess for the used access method.                  |

| D | Data memory access. See SYStem.MemAccessStop and SYStem.MemAccess for the used access method.                     |

| М | Machine privilege level                                                                                           |

| S | Supervisor privilege level. For debugger memory accesses with this access class, machine privilege level is used. |

|                   | Description                                                                                                                                                                                                                                   |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| U                 | User privilege level. For debugger memory accesses with this access class, machine privilege level is used.                                                                                                                                   |  |  |

| А                 | Absolute addressing (physical address) on SoCs with Memory Management Unit (MMU).                                                                                                                                                             |  |  |

| С                 | "Current". Do not use this access class. It might be shown by the debugger if it is unknown what access class shall be used. The actual used access class is derived from the current processor mode.                                         |  |  |

| CSR               | Control and Status Register (CSR) access.  The CSR address of this access class does always address data of maximum CSR register width XLEN. If a CSR register is smaller than the maximum size, the unused segment gets filled up with zero. |  |  |

| E                 | Allow memory access while the CPU is running. See SYStem.MemAccess, SYStem.CpuBreak and SYStem.CpuSpot. Any memory access class can be prefixed with E, if the memory supports access while the CPU is running.                               |  |  |

| VM                | Virtual Memory (memory on the debug system).                                                                                                                                                                                                  |  |  |

| SB                | System bus access. The memory accesses with this access class are performed via the "System Bus Access block" of the RISC-V Debug Module.                                                                                                     |  |  |

| DMI               | Debug Module Interface (DMI) bus access. The DMI bus is defined in the RISC-V debug specification. The address of this access class is a <i>byte address</i> . See SYStem.CONFIG RVDMIAP for details.                                         |  |  |

| APB               | APB bus access.  If the APB bus is accessible via an Arm CoreSight DAP (SoC-400), see SYStem.CONFIG APBAP.Port for details.  If the APB bus is accessible via an Arm CoreSight DAP (SoC-600), see SYStem.CONFIG APBAP.Base for details.       |  |  |

| AHB<br>NAHB, ZAHB | AHB bus access.  If the AHB bus is accessible via an Arm CoreSight DAP (SoC-400), see SYStem.CONFIG AHBAP.Port for details.  If the AHB bus is accessible via an Arm CoreSight DAP (SoC-600), see SYStem.CONFIG AHBAP.Base for details.       |  |  |

| AXI<br>NAXI, ZAXI | AXI bus access.  If the AXI bus is accessible via an Arm CoreSight DAP (SoC-400), see SYStem.CONFIG AXIAP.Port for details.  If the AXI bus is accessible via an Arm CoreSight DAP (SoC-600), see SYStem.CONFIG AXIAP.Base for details.       |  |  |

### **Combination of Several Access Classes**

It is possible to combine certain individual access classes for an access. An access class combination can consist of up to five access class specifiers. But any of the five specifiers can also be omitted.

The following **examples** will demonstrate combinations of three access classes:

- E: Allow memory access while the CPU is running

- **A:** Physical access, i.e. the MMU is bypassed.

- D: Data memory access

### Combination of three access class specifiers:

In this example, let's assume...

- You want to view the data memory from the perspective of the CPU: Use "D" access class specifier.

- You want to be able to access the data memory independent of whether the CPU is running or halted: Use "E" access class specifier.

- You want to make a physical access without any MMU address translation: Use "A" access class specifier.

When you put all three access class specifiers together, you will obtain the access class combination "EAD":

```

Data.dump EAD:0x80000000 // Physical data memory access during run-time

```

#### Combination of two access class specifiers:

In this example, let's assume...

- You want to view the data memory from the perspective of the CPU: Use "D" access class specifier.

- You want to be able to access the data memory independent of whether the CPU is running or halted: Use "E" access class specifier.

- You want to make a virtual access including MMU address translation: Do *not* use "A" access class specifier.

When you put the two access class specifiers together, you will obtain the access class combination "ED":

```

Data.dump ED:0x80000000 // Virtual data memory access during run-time

```

### One access class specifier:

In this example, let's assume...

- You want to view the data memory from the perspective of the CPU: Use "D" access class specifier.

- You do not want to be able to access the data memory while the CPU is running: Do not use "E" access class specifier.

- You want to make a virtual access including MMU address translation: Do not use "A" access class specifier.

This means in this case we wo not have a combination of access classes, but instead we simply have the access class "D":

Data.dump D: 0x80000000 // Virtual data memory access (only when stopped)

### No access class specifier:

In this example, we will see what happens when you do not specify any access class at all. In this case the memory access by the debugger will be a virtual access using the current CPU context, i.e. the debugger has the same view on memory as the CPU:

Data.dump 0x80000000 // Virtual memory access (only when stopped)

### **How to Create Valid Access Class Combinations**

There are certain rules on if and how individual access classes can be combined. Only certain access classes can be combined with each other, and they need to be combined in a certain order.

The illustrations below will show you how to combine access class specifiers for frequently-used access class combinations.

### Rules to create a valid access class combination:

- From each column of an illustration block, select only one access class specifier.

- You may skip any column but only if the column in question contains an empty square.

- Do not change the original column order. Recommendation: Put together a valid combination by starting with the left-most column, proceeding to the right.

### Memory Access Through CPU (CPU View)

The debugger uses the CPU to access memory, so the CPU carries out the accesses requested by the debugger. This can be either virtual or physical accesses. The accesses can either only happen when the CPU is stopped, or also while the CPU is running.

#### **Example combinations:**

| ΕC | ) Data        | memory        | access a    | t run-time |

|----|---------------|---------------|-------------|------------|

|    | <b>J</b> Dala | 1 IIIEIIIOI V | ี สเเเษออ ส |            |

MD Data memory access with machine privilege level

**EMD** Data memory access with machine privilege level at run-time

AP Physical program memory access

This is used to access the CSRs of a core.

## **Example combinations:**

**ECSR** CSR access at run-time

## **System Bus Access**

These accesses grant direct access to system buses, bypassing the CPU.

## **Example combinations:**

Access secure memory location via AXI at run-time **EZAXI**

System bus access of RISC-V debug module at run-time **ESB**

## **Breakpoints**

For general information about setting breakpoints, refer to the **Break.Set** command.

## **Software Breakpoints**

If a software breakpoint is used, the original instruction at the breakpoint location is temporarily patched by a breakpoint instruction (RISC-V *EBREAK* instruction). There is no restriction in the number of software breakpoints used in a debug session. However, using a software breakpoint requires both read and write access to the respective memory location.

## **On-chip Breakpoint Resources**

If on-chip breakpoints are used, the resources to set the breakpoints are provided by the hardware of the core itself.

For this purpose, a RISC-V core can have generic on-chip triggers that can either be used for on-chip instruction breakpoints or on-chip data breakpoints. These generic triggers are called "address/data match triggers". The availability of such triggers is optional, and the number of triggers that are available depends on the respective hardware of the core.

This means that on-chip instruction and on-chip data breakpoints share the number of available trigger resources among each other.

One breakpoint can require one or multiple hardware resources, depending on the complexity of the breakpoint.

**Example**: We have a core with five address/data match trigger resources, and each breakpoint requires exactly one hardware resource. We can either set five on-chip instruction breakpoints, or we could set three instruction breakpoints and two data breakpoints.

## **On-chip Breakpoints for Instruction Address**

On-chip breakpoints for instruction addresses are used to stop the core when an instruction at a certain address is executed.

The resources to set instruction breakpoints are provided by the hardware of the core. For details about the implementation and number of these breakpoints, see chapter **On-chip Breakpoint Resources**.

On-chip instruction breakpoints are particularly useful in scenarios where the program code lies in read-only memory regions such as ROM or flash, as software breakpoints cannot be used in such scenarios. Furthermore breakpoints for instruction address ranges can only be realized with on-chip breakpoints.

## **On-chip Breakpoints for Data Address**

On-chip breakpoints for data addresses are used to stop the core after a read or write access to a memory address.

The resources to set data address breakpoints are provided by the core. For details about the implementation and number of these breakpoints, see chapter On-chip Breakpoint Resources.

#### On-chip data address breakpoints with address range

Some RISC-V on-chip data address breakpoint triggers allow to set triggers for address ranges. Address ranges for on-chip breakpoint of RISC-V can be implemented in two different ways:

## Address range via address mask:

An address range can be expressed with an address mask, if the range matches the following criteria:

Let the address range be from address A to address B (B inside range), with A < B.

Let X = A XOR B (infix operator XOR: "exclusive or").

Let Y = A AND X (infix operator AND: "logical and").

Then all bits in X that equal to one have to be in consecutive order, starting from the least significant bit.

Then Y has to equal zero.

#### Address range via two addresses:

An address range can be expressed with a start address and an end address.

An address range via address mask requires less hardware resources than an address range via two addresses. If the criteria for the address mask are met then the debugger will always automatically choose the mask method, in order to save hardware resources.

#### Examples:

```

Break.Set 0x0000--0x0FFF /Read

; Address range suitable for

: address mask

Break.Set 0x0100--0x01FF /Read

; Address range suitable for

: address mask

Break.Set 0x3040--0x307F /Write

; Address range suitable for

; address mask

Break.Set 0xA000--0xB0FF /Write

; Address range suitable for

; two addresses

; Address range suitable for

Break.Set 0xA000--0xA0FD /Write

: two addresses

```

## On-chip Data Value Breakpoints

The hardware resources of the core can be used to stop the core when a specific value is read or written:

#### Data Value Breakpoint (Read):

Stop the core when a specific data value is read from a memory address.

#### Data Value Breakpoint (Write):

Stop the core when a specific data value is written to a memory address.

For more information about data value breakpoints, see the **Break.Set** command.

## **Examples for Standard Breakpoints**

Assume you have a target with

- FLASH from  $0 \times 0 = -0 \times ffff$

- **RAM from** 0x10000--0x3FFF

The command MAP.BOnchip can be used to inform the debugger for which memory regions breakpoints should only be implemented as on-chip breakpoints. That is why we mark the FLASH region as follows:

```

MAP.BOnchip 0x0--0xffff

```

#### The following shows examples for setting standard software breakpoints:

```

Break.Set P:0x20100 /Program

; Software breakpoint on

: instruction address

Break.Set main / Program

; Software breakpoint on symbol

```

## The following shows examples for setting standard on-chip breakpoints:

```

Break.Set P:0x40 /Program

; On-chip breakpoint on

; instruction address.

; Use on-chip breakpoint because

; address inside MAP.BOnchip range.

Break.Set P:0x20200 /Program

; On-chip breakpoint on

; instruction address.

/Onchip

; Use on-chip breakpoint because

; of explicit '/Onchip' option.

Break.Set P:0x40--0x48 /Program

; On-chip breakpoint on

; instruction address range

Break.Set D:0x1010 /Read

; On-chip read breakpoint on

; data address

Break.Set D:0x1020 /Write

; On-chip write breakpoint on

; data address

Break.Set D:0x1030 /ReadWrite

; On-chip read and write breakpoint

; on data address

Break.Set D:0x1010--0x101F /Read

; On-chip read breakpoint on

; data address range

Break.Set D:0x10 /Read

; On-chip read breakpoint on

; data address, combined with

/DATA.Long 0x123

; condition for read data value

```

## **Floating-Point Extensions**

The TRACE debugger for RISC-V supports the floating-point extensions of the RISC-V ISA, including both the single-precision ("F" extension) and double-precision ("D" extension) floating-point extensions.

These extensions adhere to the IEEE 754-2008 arithmetic standard. Notably, any core that supports the double-precision extension inherently supports the single-precision extension. According to the RISC-V ISA specification, a 32-bit single-precision value is stored in a 64-bit double-precision floating-point register by filling the upper 32 bits with all 1s (a process known as NaN boxing, short for "Not a Number" boxing).

The floating-point features are managed through the **FPU** (Floating-Point Unit) command group. When modifying floating-point values using the **FPU.Set** command, users can specify the desired precision for writing values.

## Examples:

```

FPU.Set F4.auto 1.4; Write to register with

; automatic detection of precision

FPU.Set F4.Single 2.7; Write to register with single-precision

FPU.Set F4.Double 3.2; Write to register with double-precision

FPU.Set F6.Single 0xABCD; Write to register with single-precision

; in hexadecimal notation

FPU.Set F6.Double 12.; Write to register with double-precision

; in decimal notation

```

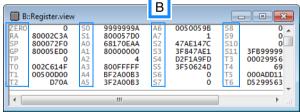

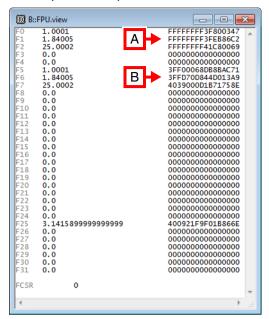

The **FPU.view** window automatically displays register values using the following conventions:

- Single-precision representation for values stored with NaN boxing.

- Double-precision representation for values stored without NaN boxing.

#### **Example:**

The following shows 64-bit floating-point registers displaying identical values in both single-precision and double-precision representations.

- A Single-precision representation

- **B** Double-precision representation

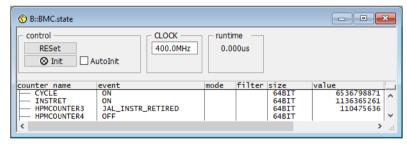

## **Hardware Performance Monitor**

The RISC-V ISA defines a so-called "Hardware Performance Monitor", which consists of several hardware counters (mcycle, minstret, mhpmcounter, ...). The existence of such a monitor and its counters is optional, so it may not be available in all RISC-V devices.

The Lauterbach **BMC** (**B**ench**M**ark **C**ounter) command group does provide control and usage of these hardware performance counters, if available on the chip:

For information about architecture-independent BMC commands, refer to "BMC" (general ref b.pdf).

## Hart State: Unavailable

The RISC-V Debug Module can flag a RISC-V hart as "unavailable", by setting the respective *allunavail/anyunavail* status bits of the *dmstatus* debug register.

The RISC-V debug specification says: "Harts may be unavailable for a variety of reasons including being reset, temporarily powered down, and not being plugged into the hardware platform."

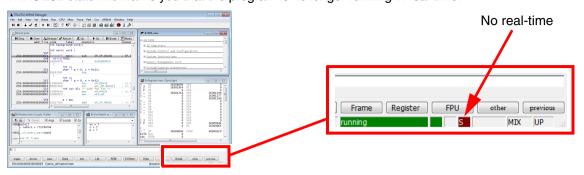

If the debugger detects that a hart is currently flagged as unavailable, then it will display "unavailable" in the bottom-right corner of the TRACE32 state line:

As long as the hart is in this state, it is not possible to manually halt the hart via the Break.direct command.

#### NOTE:

In order to poll the state of a hart, the debugger needs to have full access to all debug registers of the RISC-V debug module. This means that even when a RISC-V hart is for example in reset or power-down, then the debug IP such as RISC-V Debug Module, Debug Module Interface (DMI), etc should still be active and available to the debugger. If however the debug IP, including the JTAG connector, gets powered down as well (which is **not recommended**), then please refer to SYStem. Mode. StandBy.

## **Semihosting**

Semihosting is a technique for application programs running on a RISC-V processor to communicate with the host computer of the debugger. This way the application can use the I/O facilities of the host computer like keyboard input, screen output, and file I/O. This is especially useful if the target platform does not yet provide these I/O facilities or in order to output additional debug information in printf() style.

RISC-V semihosting is based on the "Semihosting for AArch32 and AArch64: Release 2.0" specification available here: https://github.com/ARM-software/abi-aa/blob/main/semihosting/semihosting.rst

A RISC-V semihosting call is invoked by the following semihosting trap instruction sequence:

#### Semihosting register definitions:

Operation number register: a0

Parameter register: a1

Return register: a0

Data block field size: 32bits for RV32, 64bits for RV64

There is no need to set any additional breakpoints since the ebreak instruction itself will stop the core. The debugger will restart the core after the semihosting data is processed.

Semihosting for RISC-V is enabled by **TERM.METHOD RISCVSWI** and by opening a **TERM.GATE** window for the semihosting screen output. The handling of the semihosting requests is only active when the **TERM.GATE** window does exist.

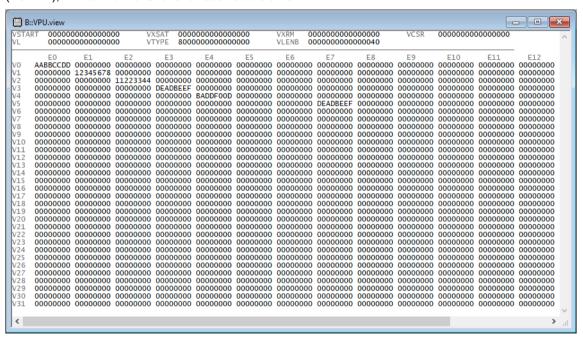

## **Vector Extension**

The Lauterbach debugger for RISC-V provides support for the vector register extension ("V" extension) of the RISC-V ISA.

The vector features are provided by the **VPU** (Vector Processing Unit) command group. This command group is only unlocked if the RISC-V target does support the vector extension.

The **VPU.view** window does display the vector registers. The vector register width *VLEN* is automatically detected by the debugger, and the width of the vector registers in the **VPU.view** window is adjusted accordingly.

As RISC-V vector registers (v0 - v31) can be quite large, the debugger displays them in sub-elements (E0 - En), with a width of 32bits for each sub-element.

When modifying values with **VPU.Set**, the user can write to each sub-element (*E0 - En*) of a vector register individually.

## Example:

```

VPU.Set V8_E2 0x12345678 ; Write to vector register v8, sub-element #2

```

## **RISC-V Trace Standards**

## **RISC-V Trace Specifications**

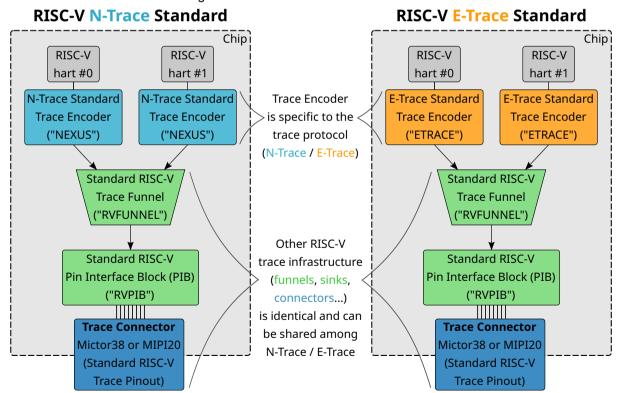

The Lauterbach RISC-V trace tools are mainly based on the official RISC-V trace standards. There are two RISC-V trace standards:

- RISC-V N-Trace (Nexus-based Trace) Standard

- RISC-V E-Trace (Efficient Trace) Standard

Each of these two overall trace standards are composed of several sub-specifications, and each sub-specification is a separate document. Some of these sub-specifications are exclusive to either N-Trace or E-Trace, whereas some other sub-specifications are applicable to and shared among both N-Trace and E-Trace.

The RISC-V N-Trace Standard is composed of the following sub-specifications:

- RISC-V N-Trace (Nexus-based Trace) Specification

- RISC-V Trace Control Interface Specification

- RISC-V Trace Connectors Specification

The RISC-V E-Trace Standard is composed of the following sub-specifications:

- RISC-V E-Trace (Efficient Trace) Specification

(Older versions of this specification (up to v1.0) were called "RISC-V Processor Trace

Specification", but starting with v2.0.0 it was renamed to make it distinguishable from N-Trace)

- RISC-V Unformatted Trace & Diagnostic Data Packet Encapsulation Specification

- RISC-V Trace Control Interface Specification

- RISC-V Trace Connectors Specification

The following is a summary of the respective sub-specifications:

|         | RISC-V        | RISC-V        | RISC-V        | RISC-V        | RISC-V        |

|---------|---------------|---------------|---------------|---------------|---------------|

|         | N-Trace       | E-Trace       | Unformatted   | Trace Control | Trace         |

|         | Specification | Specification | Trace Packet  | Interface     | Connectors    |

|         |               |               | Encapsulation | Specification | Specification |

|         |               |               | Specification |               |               |

| RISC-V  |               |               |               |               |               |

| N-Trace | •             |               |               | •             | •             |

| RISC-V  |               |               |               |               |               |

| E-Trace |               | •             | •             | •             | •             |

The RISC-V trace standards define the following RISC-V trace IP blocks:

- RISC-V N-Trace Trace Encoder (see SYStem.CONFIG.NEXUS)

- RISC-V E-Trace Trace Encoder (see SYStem.CONFIG.RVETRACE)

- RISC-V Trace Funnel (see SYStem.CONFIG.RVFUNNEL)

- RISC-V SRAM On-Chip Trace Sink (see SYStem.CONFIG.RVSRAMTRACE)

- RISC-V System Memory On-chip Trace Sink (see SYStem.CONFIG.RVSMEMTRACE)

- RISC-V Pin Interface Block (PIB) Off-chip Trace Sink (see SYStem.CONFIG.RVPIB)

- RISC-V ATB Bridge (see SYStem.CONFIG.RVATBBRIDGE)

The N-Trace Trace Encoder is only applicable to the N-Trace Standard.

The E-Trace Trace Encoder is only applicable to the E-Trace Standard.

All other RISC-V trace IP blocks that are mentioned in the list above are applicable to both, the N-Trace Standard and the E-Trace Standard.

The following illustration shows two example setups to demonstrate which IP blocks are specific to and which IP blocks are shared among the two RISC-V trace standards:

Each of these RISC-V trace IP blocks does have its own separate **trace control interface block**. Each trace control interface block is a set of 32-bit registers occupying an address space of up to 4KB. The base address of each trace control interface block must be aligned on the 4KB boundary.

| N- | Trace |

|----|-------|

|    | HUCC  |

E-Trace

## **Quick Start for Trace Configuration Basics**

The configuration of trace requires several steps, which vary and depend on the trace hardware of your chip. This chapter gives a brief overview over the most common trace configuration steps:

#### 1. Configuration of the debug IP.

Before the configuration of the trace IP, it is necessary to configure the debug IP first. See for example chapter "Quick Start of the JTAG Debugger" for details.

#### 2. Define trace source(s).

```

SYStem.CONFIG.NEXUS.<sub_cmd>

or

SYStem.CONFIG.RVETRACE.<sub_cmd>

```

These two command groups can be used to define and configure the existence of an N-Trace and/or E-Trace **trace encoder** in the system, and its location in the system.

Each RISC-V hart that can be traced does have its own trace encoder.

## 3. Define trace funnel(s).

```

SYStem.CONFIG.RVFUNNEL.<sub cmd>

```

If the trace system does have one or more RISC-V trace funnels, then the above command group defines and configures the existence of a RISC-V trace funnel, and its location in the system.

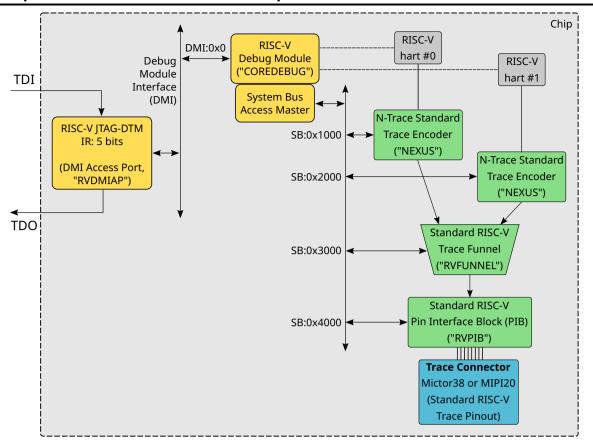

If the system does have more than one trace encoder / more than one trace source (i.e. if it is a multicore trace system), then it most probably does have a trace funnel.

#### 4. Define trace sink(s).

```

SYStem.CONFIG.RVSRAMTRACE.<sub_cmd>

or

SYStem.CONFIG.RVSMEMTRACE.<sub_cmd>

or

SYStem.CONFIG.RVPIB.<sub_cmd>

```

The above command groups define and configure the existence of one or more trace sink(s), and their respective location in the system.

The RISC-V on-chip trace sink categories are SRAM and SMEM trace sink. The RISC-V off-chip trace sink is PIB.

Each trace system must have at least one trace sink.

#### 5. **Define off-chip trace port.**

```

SYStem.CONFIG.TRACEPORT.<sub_cmd>

```

If the system has an off-chip trace sink, then the above command defines the type of the trace port and the off-chip trace sink on the chip that is connected to it.

This command is only applicable to some off-chip trace sinks, but it is never applicable to on-chip trace sinks.

#### Define trace method.

```

Trace.METHOD < method>

```

The above command selects the trace method that you want to use. This is particularly important, if your system has more than one (type of) trace sink.

## 7. Configure trace source(s).

```

NEXUS.<sub_cmd>

or

RVETRACE.<sub_cmd>

```

The above command groups set the configuration settings of the control registers of the trace source (e.g. N-Trace trace encoder or E-Trace trace encoder).

The command group can only be used, if the respective trace source has previously been defined (see steps above).

## 8. Configure trace sink(s).

```

RVPIB. < sub cmd>

```

The above command group sets the configuration settings of the control registers of the trace sink.

The command group can only be used, if the respective trace sink has previously been defined (see steps above).

#### 9. Initialize trace sink(s).

#### Trace.Init

The above command initializes the trace sink and clears any previously recorded trace data.

## **Quick Start for Trace Configuration Examples**

This chapter shows configuration examples for certain RISC-V trace setups:

- Example A: Single-core N-Trace to On-chip Trace Sink

- Example B: Multi-core N-Trace to Off-chip Trace Sink

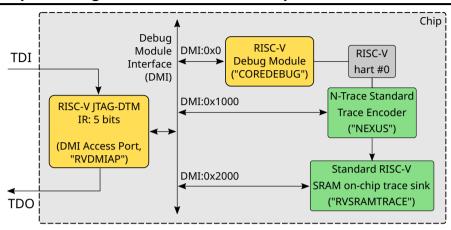

## **Example A: Single-core N-Trace to On-chip Trace Sink**

## Debugger configuration example

```

;----- Debug configuration -----

SYStem.CPU <cpu>

SYStem.CONFIG.RVDMIAP1.DebugSource DebugPort

; JTAG-DTM / RVDMIAP

SYStem.CONFIG.RVDMIAP1.IRWIDTH 5.

SYStem.CONFIG.RVDMIAP1.IRPRE 0.

SYStem.CONFIG.RVDMIAP1.IRPOST 0.

SYStem.CONFIG.RVDMIAP1.DRPRE 0.

SYStem.CONFIG.RVDMIAP1.DRPOST 0.