# **ARM-ETM Training**

### **TRACE32 Online Help**

**TRACE32 Directory**

**TRACE32 Index**

| TRACE32 Training                                    |    |

|-----------------------------------------------------|----|

| Training ARM-ETM                                    |    |

| ARM-ETM Training                                    | 1  |

| History                                             | 4  |

| ETM Setup                                           | 5  |

| ETM Versions                                        | 5  |

| Main Setup Windows                                  | 6  |

| ETM.state Window                                    | 6  |

| Trace.state Window                                  | 7  |

| ETMv1                                               | 8  |

| Interface and Trace Protocol                        | 8  |

| Basic Setup                                         | 10 |

| What can I do to prevent a FIFO overflow (ETMv1.x)? | 14 |

| ETMv3                                               | 15 |

| Interface and Protocol                              | 15 |

| Basic Setups                                        | 17 |

| Additional Settings                                 | 19 |

| PTM (aka. PFT)                                      | 26 |

| Block Diagram                                       | 27 |

| Protocol Description                                | 29 |

| Basic Setup                                         | 31 |

| Additional Settings                                 | 36 |

| FLOWERROR                                           | 37 |

| Diagnostic Commands                                 | 38 |

| Displaying the Trace Contents                       | 40 |

| Source for the Recorded Trace Information           | 40 |

| Sources of Information for the Trace Display        | 42 |

| Influencing Factors on the Trace Information        | 43 |

| ETM Features and Settings                           | 44 |

| Settings in the TRACE32 Trace Configuration Window  | 46 |

| States of the Trace                                 | 56 |

| The AutoInit Command                                | 57 |

| Basic Display Commands                              | 58 |

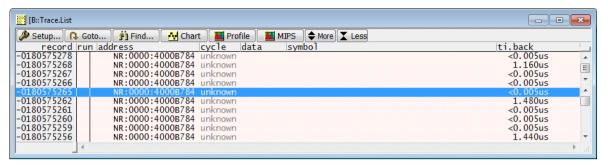

| Default Listing                                     | 58 |

| Basic Formatting                                      | 59  |

|-------------------------------------------------------|-----|

| Correlating the Trace Listing with the Source Listing | 60  |

| Browsing through the Trace Buffer                     | 61  |

| Display Items                                         | 62  |

| Default Display Items                                 | 62  |

| Further Display Items                                 | 65  |

| Find a Specific Record                                | 69  |

| Belated Trace Analysis                                | 71  |

| Save the Trace Information to an ASCII File           | 72  |

| Postprocessing with TRACE32 Instruction Set Simulator | 73  |

| Export the Trace Information as ETM Byte Stream       | 76  |

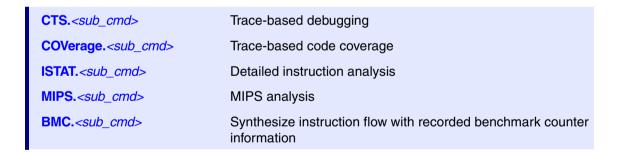

| Trace-based Debugging (CTS)                           | 77  |

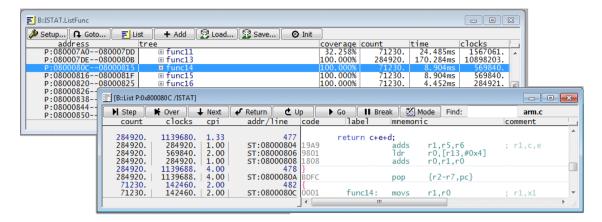

| Forward and Backward Debugging                        | 78  |

| CTS Technique                                         | 83  |

| Belated Trace-based Debugging                         | 85  |

| HLL Analysis of the Trace Contents                    | 86  |

| Details on each HLL Instruction                       | 86  |

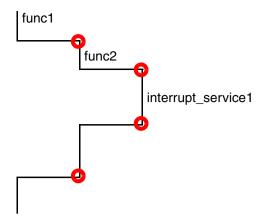

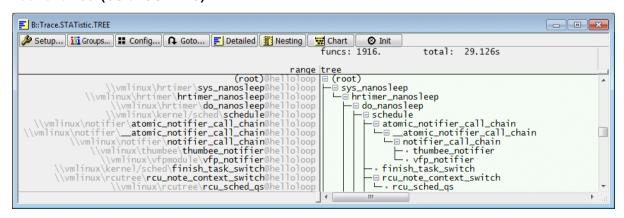

| Function Nesting                                      | 87  |

| Trace Control by Filter and Trigger                   | 90  |

| Context                                               | 90  |

| Filters and Trigger by Using the Break.Set Dialog     | 94  |

| Examples for TraceEnable on Read/Write Accesses       | 95  |

| Examples for TraceEnable on Instructions              | 99  |

| Example for TraceData                                 | 103 |

| Example for TraceON/TraceOFF                          | 104 |

| Example for BusTrigger                                | 110 |

| Example for BusCount                                  | 111 |

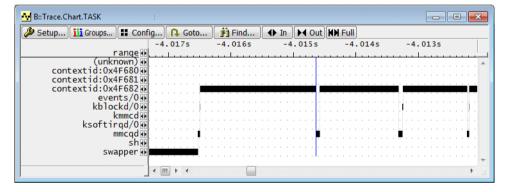

| OS-Aware Tracing                                      | 113 |

| OS (No Dynamic Memory Management)                     | 113 |

| Activate the TRACE32 OS Awareness (Supported OS)      | 113 |

| Exporting the Task Switches (OS)                      | 116 |

| Belated Trace Analysis (OS)                           | 121 |

| Enable an OS-aware Tracing (Not-Supported OS)         | 122 |

| OS+MMU (Dynamic Memory Management)                    | 123 |

| Activate the TRACE32 OS Awareness                     | 123 |

| Exporting the Process/Thread-ID (OS+MMU)              | 124 |

| Belated Trace Analysis                                | 130 |

| Specific Write Access vs. Context ID Packet           | 132 |

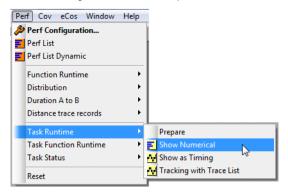

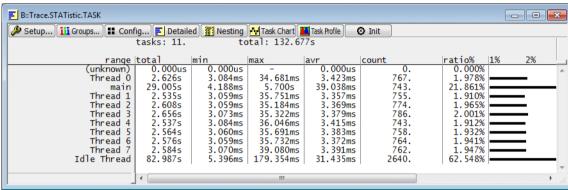

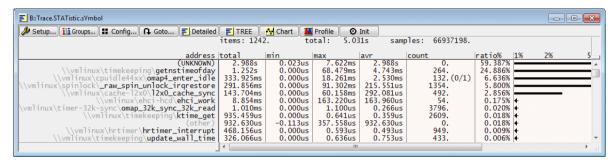

| Task Statistics                                       | 133 |

| Ended Processes (OS+MMU)                              | 134 |

| Context ID Comparator                                 | 135 |

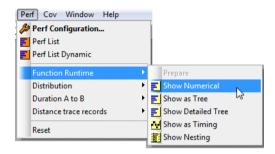

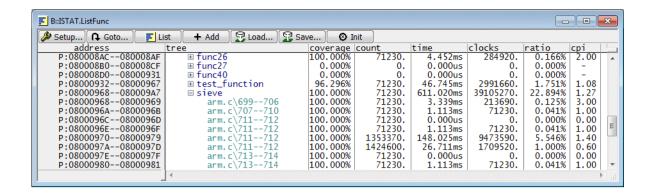

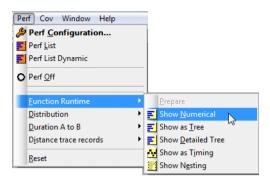

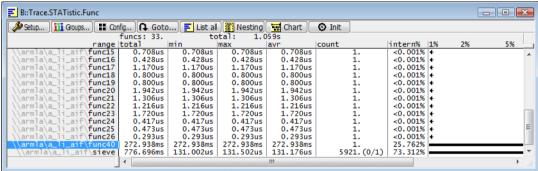

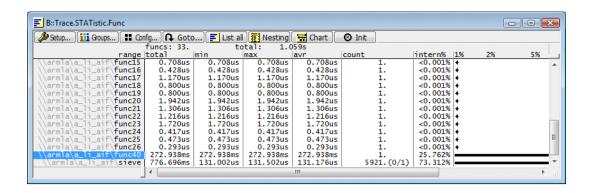

| Function Run-Times Analysis                           | 137 |

|                                                              | 40- |

|--------------------------------------------------------------|-----|

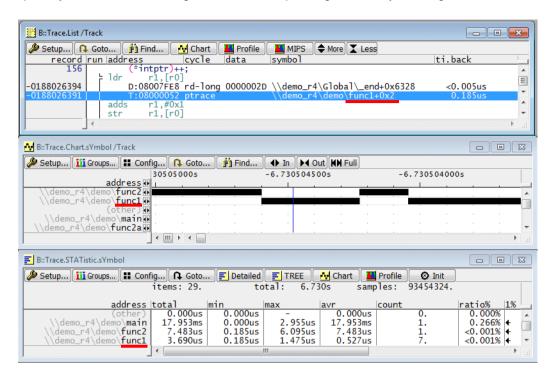

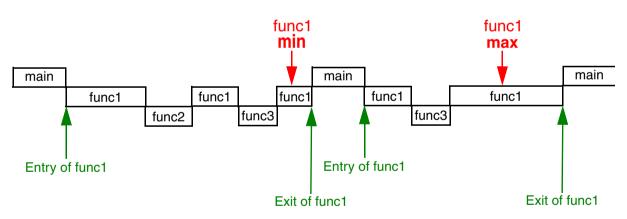

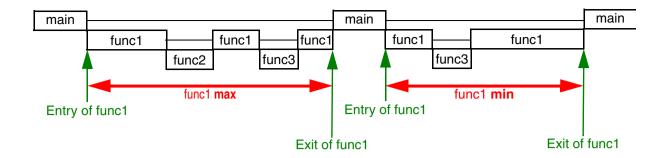

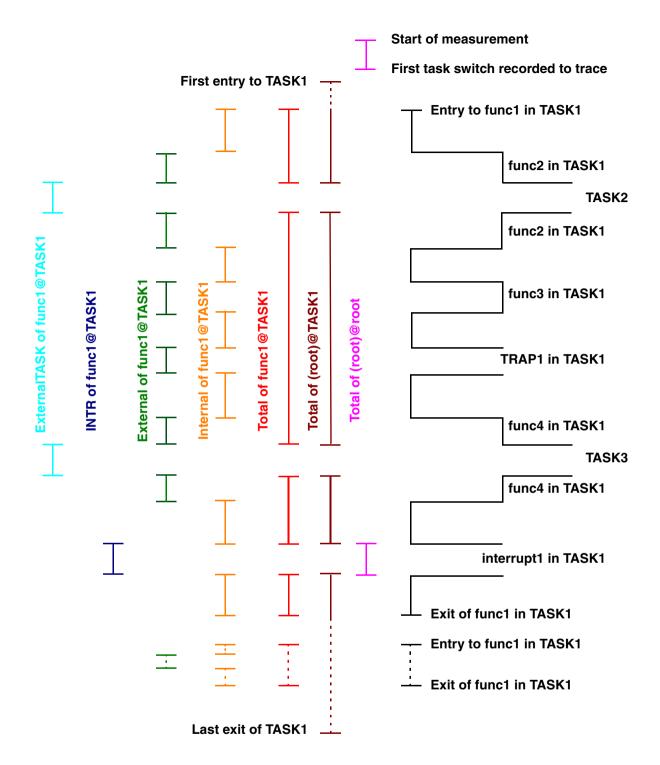

| Flat vs. Nesting Analysis                                    | 137 |

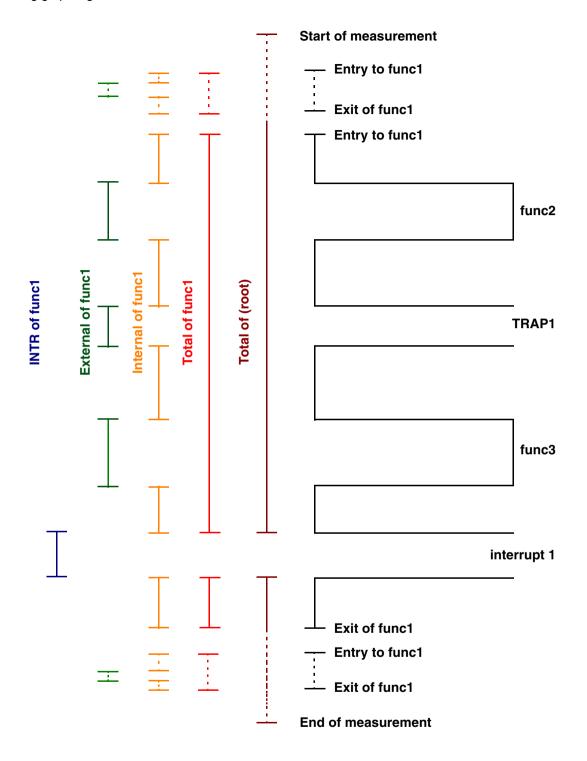

| Basic Knowledge about Flat Analysis                          | 138 |

| Basic Knowledge about Nesting Analysis                       | 139 |

| Summary                                                      | 141 |

| Flat Analysis                                                | 142 |

| Optimum ETM Configuration (No OS or OS)                      | 142 |

| Optimum ETM Configuration (OS+MMU)                           | 143 |

| Dynamic Program Behavior                                     | 144 |

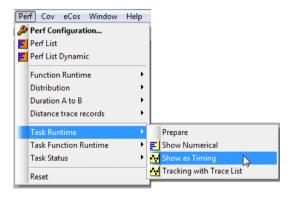

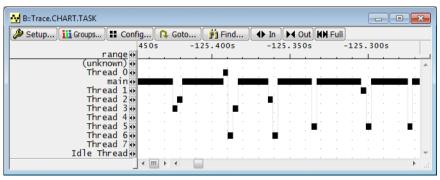

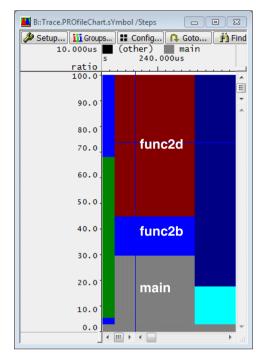

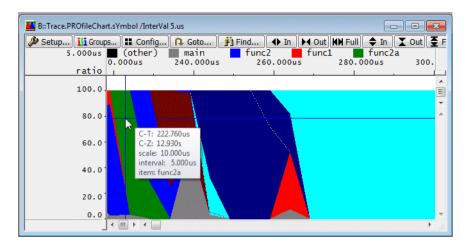

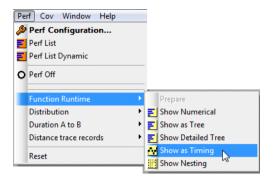

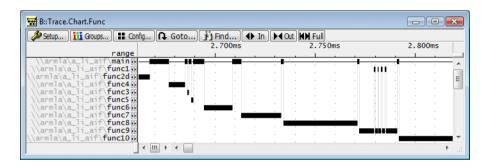

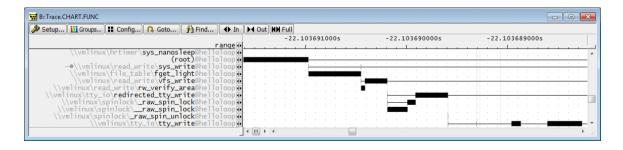

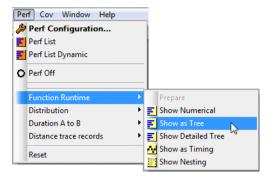

| Function Timing Diagram                                      | 151 |

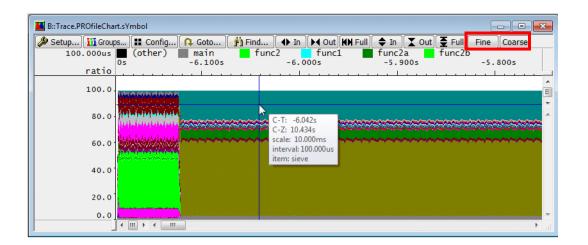

| Hot-Spot Analysis                                            | 157 |

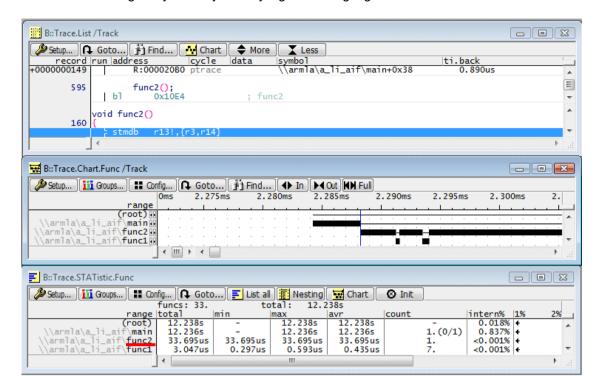

| Nesting Analysis                                             | 165 |

| Restrictions                                                 | 165 |

| Optimum ETM Configuration (No OS)                            | 165 |

| Optimum ETM Configuration (OS or OS+MMU)                     | 166 |

| Items under Analysis                                         | 167 |

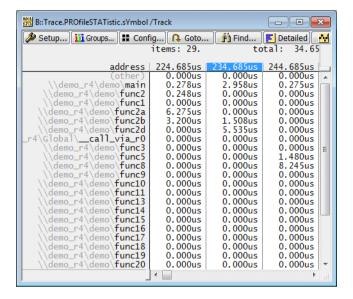

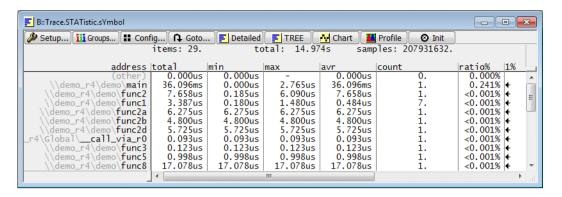

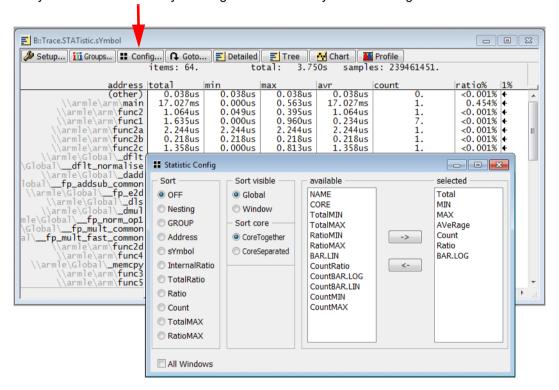

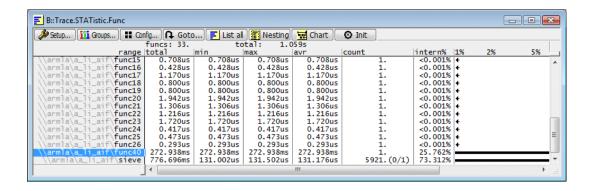

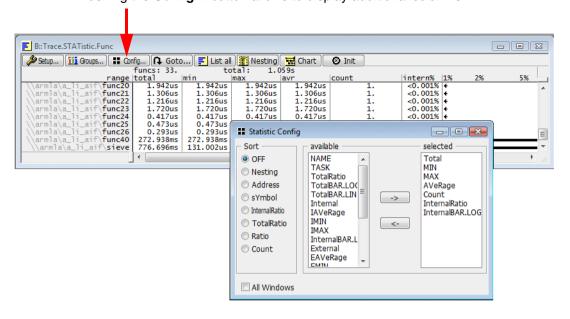

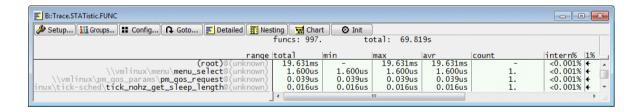

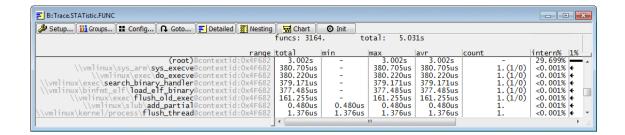

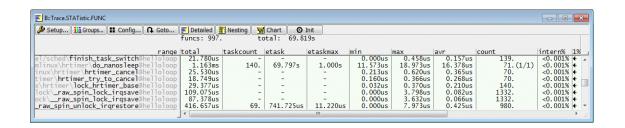

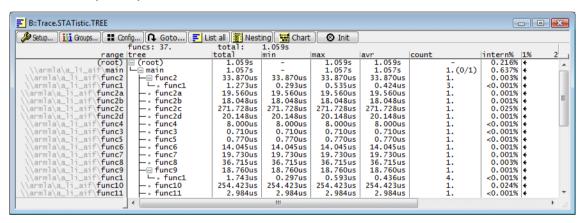

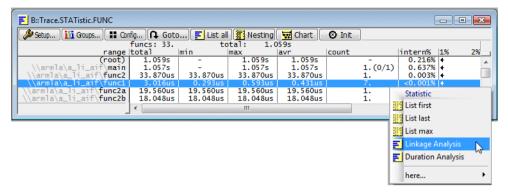

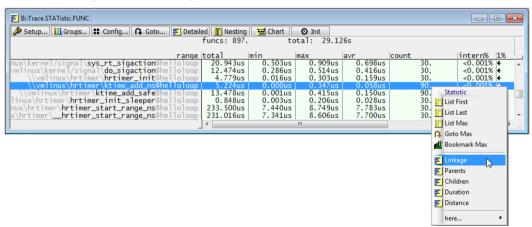

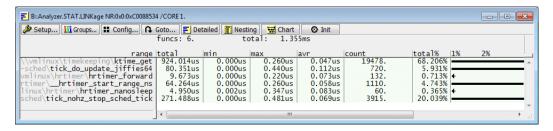

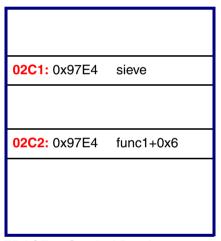

| Numerical Nested Function Run-time Analysis for all Software | 170 |

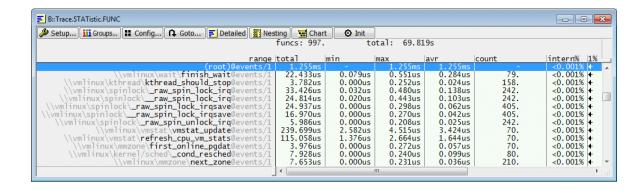

| Additional Statistics Items for OS or OS+MMU                 | 177 |

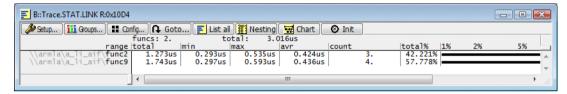

| More Nesting Analysis Commands                               | 181 |

| Trace-based Code Coverage                                    | 184 |

| Optimum ETM Configuration (No OS or OS)                      | 184 |

| Optimum ETM Configuration (OS+MMU)                           | 184 |

# **ARM-ETM Training**

Version 25-Aug-2020

# **History**

24-Aug-2020 Chapter "Code Coverage" was updated. Cross references to "Application Note for Trace-Based Code Coverage" (app\_code\_coverage.pdf) was added. Chapter "Code Coverage" now only contains some hints for the setups for ARM-ETM.

## **ETM Setup**

#### **ETM Versions**

The parallel ETM is available in the following versions:

- ETMv1.x for ARM7 and ARM9

- ETMv3.x for ARM11

- ETMv3.x CoreSight Single for ARM9 and ARM11

- ETMv3.x CoreSight for ARM9, ARM11, Cortex-M3/M4/M23, Cortex-R4/R5, Cortex-A5/A7

- PTM for Cortex-A9/A15/A17

- ETMv4 for Cortex-R7/R8/R52, Cortex-M7/M33 and Cortex-A3x/A5x/A7x (Cortex-A32/A35/A53/A55/A57/A72/A73/A75)

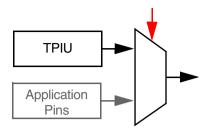

The ETM trace information can be stored internally in an onchip memory (ETB, ETF, ETR) or exported via a trace port interface (TPIU) to an external recording device (PowerTrace, CombiProbe, µTrace). Using internal memory for trace recording is also called "onchip trace". Using an external recording device is also called "offchip trace"

Chips supporting "offchip trace" usually export data via a parallel trace port: Via up to 40 pins on the chip the trace data is transferred to the PowerTrace.

Some modern Cortex-A and Cortex-R chips support also the export of the data via a High Speed Serial Trace Port (HSSTP)

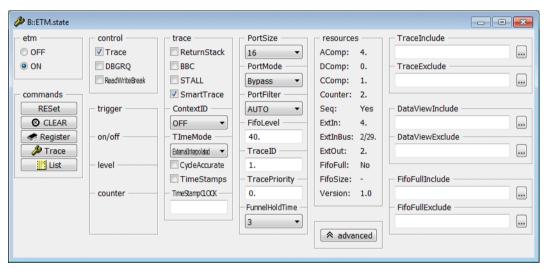

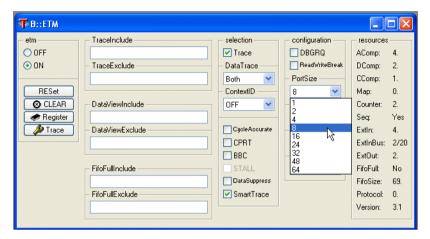

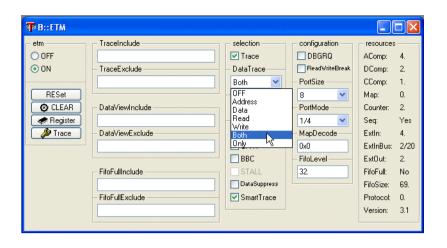

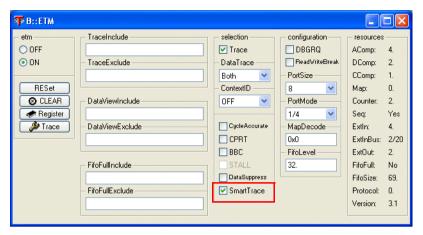

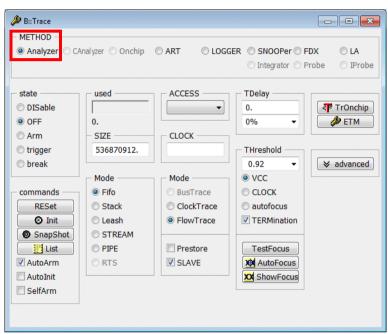

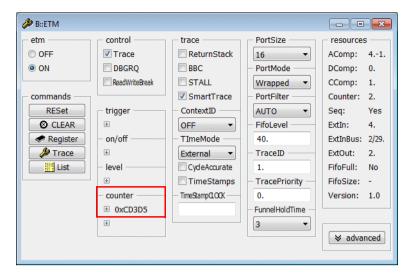

#### **ETM.state Window**

The ETM.state window allows to configure the ETM/PTM and the TPIU.

The JTAG interface is use to configure the ETM/PTM and the TPIU.

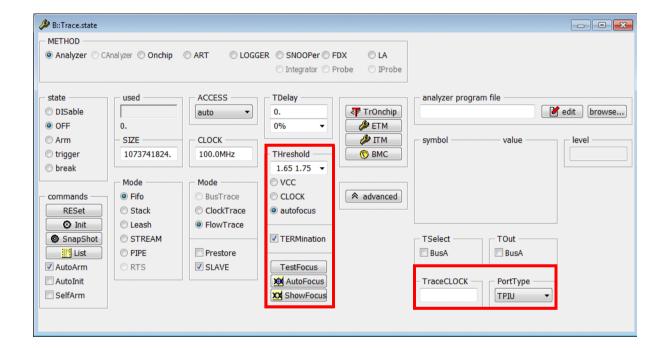

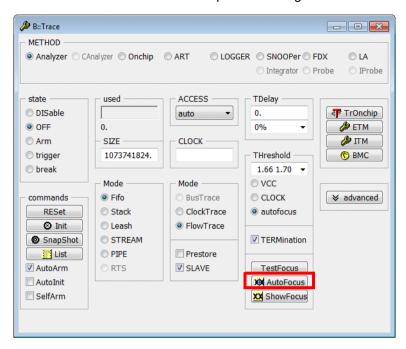

The Trace.state window allows to configure the TRACE32 Preprocessor AutoFocus II.

This chapter is only relevant if you have an ARM7 or ARM9 chip with ETMv1.

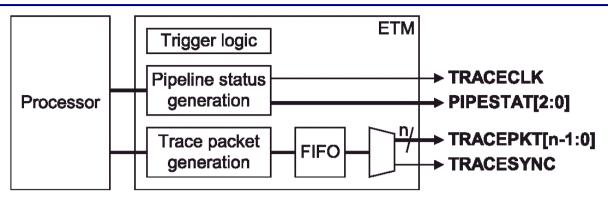

#### **Interface and Trace Protocol**

| PIPESTAT | Pipeline status pins provide a cycle-by-cycle indication of what is happening in the execute stage of the processor pipeline (instruction executed, branch executed etc.). |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRACEPKT | Trace packets (broadcast address and data information)                                                                                                                     |

| TRACECLK | ETM clock                                                                                                                                                                  |

Trace packets contain the following information:

- Address information when the processor branches to a location that cannot be directly inferred from the source code. When addresses are broadcast, high-order bits that have not changed are not broadcast.

- Data accesses that are indicated to be of interest (only data, only addresses, data and addresses).

The maximum sampling time for the program and data flow trace depends mainly

- on the size of the trace buffer

- the CPU clock

because the pipeline status information has to be sampled every clock cycle.

| ETM signals      |                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| TS               | Trace synchronization signal                                                                                               |

| PS[02]           | Pipeline status                                                                                                            |

| TP<br>TPH<br>TPL | Trace packets (depending on PortSize) Trace packets high byte (PortSize=16 only) Trace packets low byte (PortSize=16 only) |

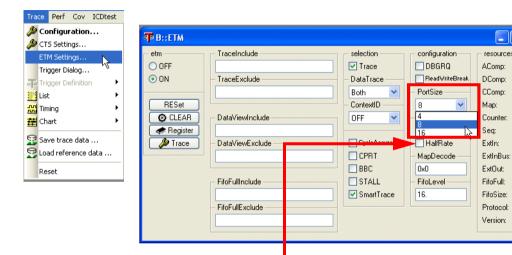

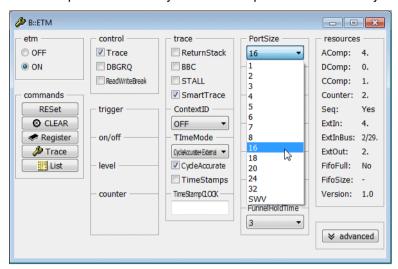

#### Port Size and Port Mode for ETMv1.x for ARM7/ARM9

1. Define the ETM port size.

TRACEPKT can be either 4, 8 or 16 bit.

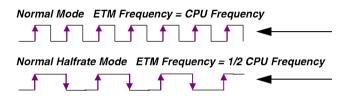

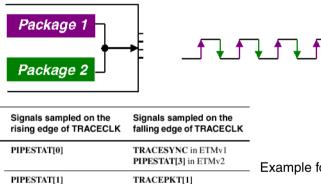

2. Define if your ETM is working in *Halfrate Mode* or not.

In Halfrate Mode trace information is broadcast on the rising and falling edge of TRACECLK.

Trace information is only broadcast on the rising edge of TRACECLK

Trace information is broadcast on the rising and falling edge of TRACECLK

4.

2.

0.

8.

2.

Yes

4.

1.

7

1.3

Yes

resources

Switch to ON if ETM is working in Halfrate mode

#### 3. Define the mode of the ETM port.

**Normal Mode:** one trace line is output via one trace port pin. HalfRate mode is supported in normal mode.

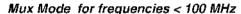

**Multiplexed Mode:** the multiplexed mode can be used to save trace lines; 2 trace lines are multiplexed to a single trace port pin.

fewer trace data lines needed

PIPESTAT[2]

TRACEPKT[0]

TRACEPKT[2]

TRACEPKT[3]

Example for a 4-pin trace connector

**Demultiplexed Mode:** the demultiplexed mode is used to reduce the switching rate for the trace port; each trace line is split across 2 trace port pins. HalfRate mode is supported in demultiplexed mode.

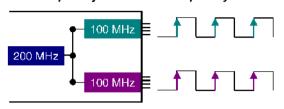

#### DeMux Mode for frequencies > 100 MHz ETM Frequency = 1/2 CPU Frequency

Table 7-6 Demultiplexed four-bit connector pinout

Example for a 4-bit trace connector

| Pin | Signal name                                    | Pin | Signal name                                    |

|-----|------------------------------------------------|-----|------------------------------------------------|

|     |                                                |     |                                                |

| 38  | PIPESTAT_A[0]                                  | 37  | PIPESTAT_B[0]                                  |

| 36  | PIPESTAT_A[1]                                  | 35  | PIPESTAT_B[1]                                  |

| 34  | PIPESTAT_A[2]                                  | 33  | PIPESTAT_B[2]                                  |

| 32  | TRACESYNC_A in ETMv1<br>PIPESTAT_A[3] in ETMv2 | 31  | TRACESYNC_B in ETMv1<br>PIPESTAT_B[3] in ETMv2 |

| 30  | TRACEPKT_A[0]                                  | 29  | TRACEPKT_B[0]                                  |

| 28  | TRACEPKT_A[1]                                  | 27  | TRACEPKT_B[1]                                  |

| 26  | TRACEPKT_A[2]                                  | 25  | TRACEPKT_B[2]                                  |

| 24  | TRACEPKT_A[3]                                  | 23  | TRACEPKT_B[3]                                  |

| 22  | No connect                                     | 21  | nTRST                                          |

| 20  | No connect                                     | 19  | TDI                                            |

| 18  | No connect                                     | 17  | TMS                                            |

| 16  | No connect                                     | 15  | тск                                            |

| 14  | VSupply                                        | 13  | RTCK                                           |

| 12  | VTRef                                          | 11  | TDO                                            |

| 10  | EXTTRIG                                        | 9   | nSRST                                          |

| 8   | DBGACK                                         | 7   | DBGRQ                                          |

| 6   | TRACECLK                                       | 5   | GND                                            |

| 4   | No connect                                     | 3   | No connect                                     |

| 2   | No connect                                     | 1   | No connect                                     |

| Demuxed  | 4-bit demultiplexed trace port (one mictor connector to target)          |

|----------|--------------------------------------------------------------------------|

| Demuxed2 | 8- and 16-bit demultiplexed trace port (two mictor connectors to target) |

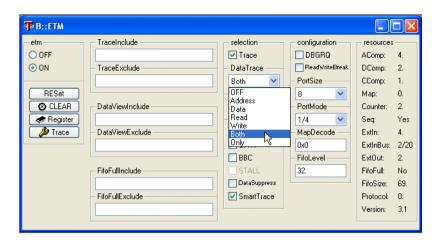

| DataTrace (ETMv1) |                                                                      |

|-------------------|----------------------------------------------------------------------|

| OFF               | No information about data accesses is broadcast.                     |

| Address           | Only the address information for data accesses is broadcast.         |

| Data              | Only the data information for data accesses is broadcast.            |

| Read              | The address and data information is broadcast for read accesses.     |

| Write             | The address and data information is broadcast for write accesses.    |

| Both              | The address and data information is broadcast for all data accesses. |

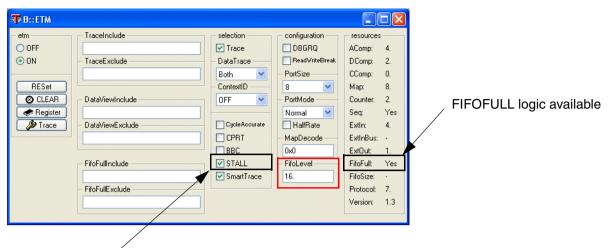

If a FIFOFULL logic is implemented on your ETM, it is possible to stall the processor when a FIFO overflow is likely to happen.

Stall the processor if a FIFO overflow is likely to happen

The ETM does not provide any information to help you to find out how big is the performance loss caused by stalling the processor.

ARM7TMI, ARM720T, ARM920T and ARM922T do not support the stalling of the core when the ETM target FiFo is (almost) full. (You can set the option, but it won't have an effect.)

ETM.STALL ON is supported by ARM926EJ-S, ARM946E-S and ARM966E-S.

This chapter is only relevant if you have a chip with an ARM ETMv3.

This are usually chips with a Cortex-M3/M4/M23, Cortex-R4/R5, Cortex-A5/A7/A8, ARM9 or ARM11 core.

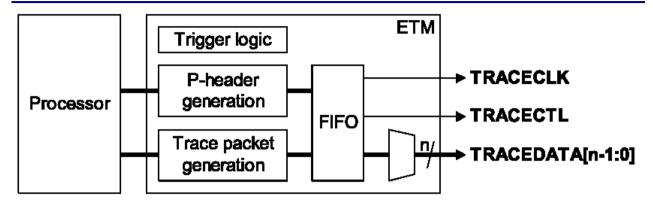

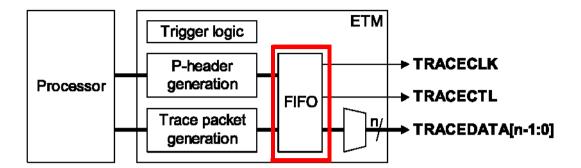

#### Interface and Protocol

| TRACECLK         | Trace clock                                                                         |

|------------------|-------------------------------------------------------------------------------------|

| TRACECTL         | Trace control indicates if the trace information is valid.                          |

| TRACEDATA[n-1:0] | Trace packets (broadcast pipeline status information, address and data information) |

Trace packets contain the following information:

- Information about the execution of instructions.

- Address information when the processor branches to a location that cannot be directly inferred from the source code. When addresses are broadcast, high-order bits that have not changed are not broadcast.

- Data accesses that are indicated to be of interest (only data, only addresses, data and addresses)

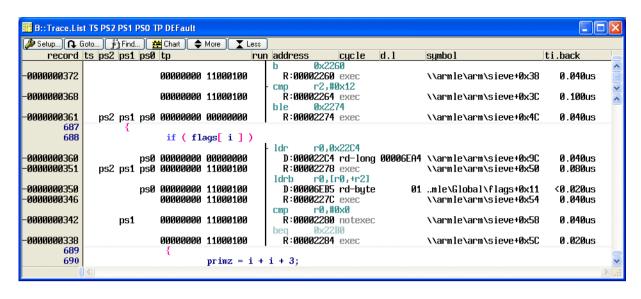

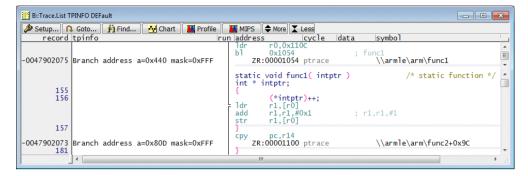

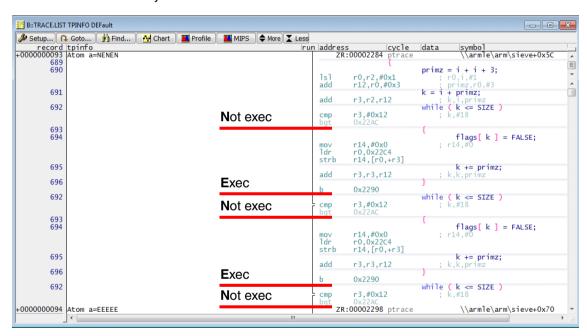

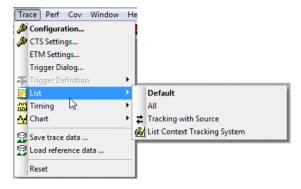

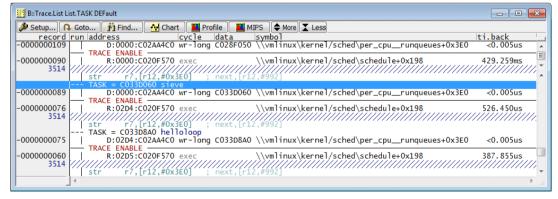

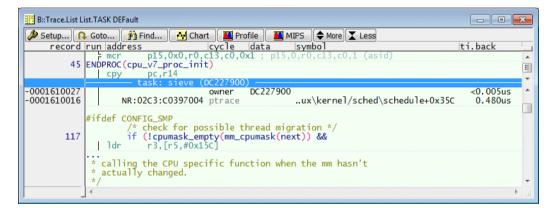

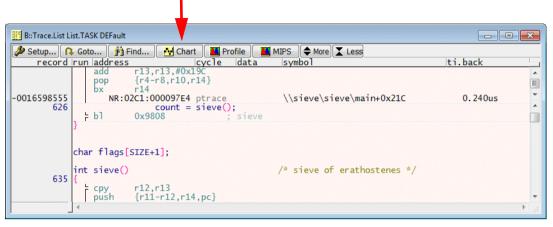

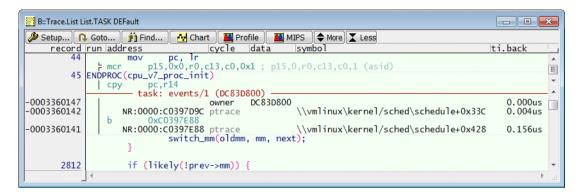

#### Trace.List TP DEFault

Due to the fact that the information about the execution of instructions is broadcasted by trace packets, the maximum sampling time depends on the number of broadcasted packages.

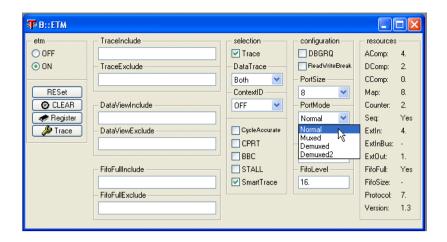

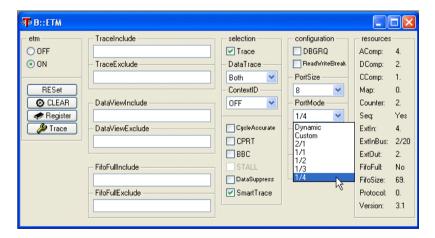

#### Port Size and Port Mode for ETMv3.x for ARM11

#### 1. Define the ETM port size

TRACEDATA can use 1..32 pins (48 and 64 pins port size is not supported yet).

#### 2. Define the mode for the ETM port

The ETMv3.x works always in half-rate mode.

The port mode defines the relation <etm\_clock>/<cpu\_clock>.

| DataTrace (ETMv3) |                                                                                                                                     |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| OFF               | No data accesses are traced. Only program flow is traced.                                                                           |  |

| ON                | Both address and data information of for all data accesses (Read and write accesses) are traced (and the program flow).             |  |

| Read              | Both address and data for read accesses are traced (and the prog. flow).                                                            |  |

| Write             | Both address and data for write accesses are traced (and the prog. flow).                                                           |  |

| Address           | The addresses of all read/write accesses are traced (and the program flow), but not the data value, which has been read or written. |  |

| ReadAddress       | The addresses of all data read accesses are traced (and the prog. flow).                                                            |  |

| WriteAddress      | The addresses of all data write accesses are traced (and the prog. flow).                                                           |  |

| Data              | The data values of all read/write accesses are traced (and the program flow), but not the addresses of the read/write accesses.     |  |

| ReadData          | Data values of all read accesses are traced (and the program flow).                                                                 |  |

| WriteData         | Data values of all write accesses are traced (and the program flow).                                                                |  |

| Only              | Only data is traced (address and data of all read/write accesses) but program flow is not traced.                                   |  |

| OnlyAddress       | Only data addresses are traced (address of all read/write accesses, but no data). Program flow is not traced.                       |  |

| OnlyData          | Only data values are traced (data of all read/write accesses, but no addresses). Program flow is not traced.                        |  |

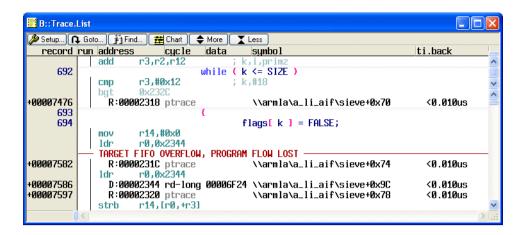

#### **FIFO Overflow**

- Broadcasting the program flow requires usually a low bandwidth and can be done without any problem.

- Broadcasting the data flow generates much more traffic on the trace port. In order to prevent an

overloading of the trace port a FIFO is connected upstream of TRACEPKT/TRACEDATA. This

provides intermediate storage for all trace packets that cannot be output via

TRACEPKT/TRACEDATA immediately.

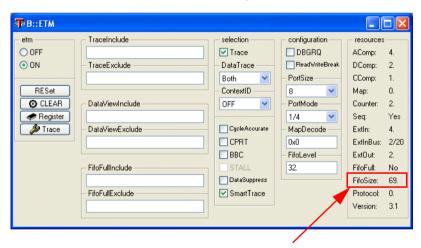

The ETMv3.x provides the FifoSize in a ETM configuration register

Under certain circumstances it is possible that so much trace information is generated, that the FIFO overflows.

If a FIFOFULL is likely to happen, the ETM suppresses the output of the data flow information.

Suppress data flow information if a FIFO overflow is likely to happen

The data suppression is not indicated in the trace.

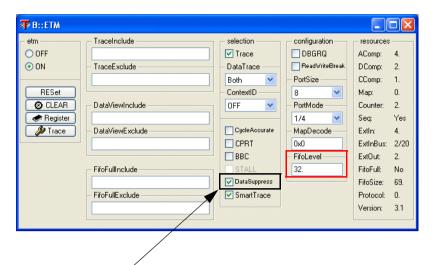

You can define a FifoLevel. If less the FifoLevel bytes are empty in the FIFO:

- The processor is stalled until the number of empty bytes is higher the FifoLevel again (ETMv1.x).

- No data information is broadcasted until the number of empty bytes is higher the FifoLevel again (ETMv3.x)

Recommendation for FifoLevel is ~2/3 of the FIFO size.

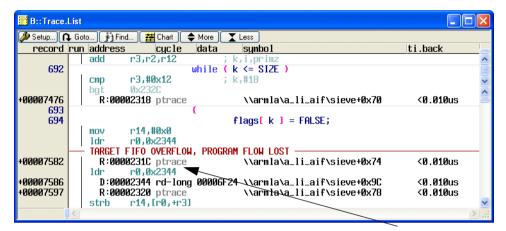

No further trace packets are accepted by the FIFO if a FIFO overflow occurs.

The ETM signals a FIFO overflow via the pipeline information and ensures, that the FIFO is completely emptied. Once the FIFO memory is ready to receive again trace packets:

- A Trace restarted after FIFO overflow is output via the pipeline information

- The full address of the instruction just executed is output.

Trace restarted after FIFO overflow

#### What can I do to reduce the risk of a FIFO overflow?

- Set the correct PortSize.

- Restrict DataTrace to read cycles (write accesses can be reconstructed via CTS).

- Restrict DataTrace to write cycles (a FIFO overflow becomes less likely).

- Reduce the broadcast of TraceData information by using a trace filter.

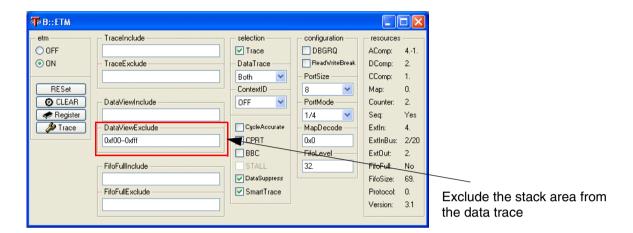

- Exclude the stack area from the data trace.

• Stall the core / supress the data flow when a FIFO overflow is likely to happen.

The gaps in the trace recording resulting from FIFO overflow can be reconstructed in most cases by using the SmartTrace and CTS.

It is not possible to reconstruct:

- Exceptions occurring in the trace gaps.

- Port reads occurring in the trace gaps.

## PTM (aka. PFT)

PTM stands for Program Trace Macrocell PTM is also known as PFT. PFT stands for Program Flow Trace.

PTM offers a stronger trace compression comparing to ETMv3 but does not offer any kind of data trace (neither data address nor data value)

The PTM is only used for Cortex-A9, Cortex-A15 and Cortex-A17 processor cores.

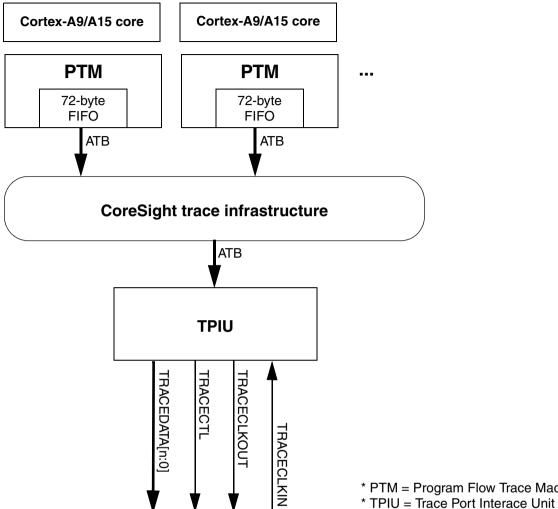

Simplified block diagram for off-chip trace with parallel interface, training-relevant components only:

<sup>\*</sup> PTM = Program Flow Trace Macrocell

<sup>\*</sup> ATB = AMBA Trace Bus

| TRACEDATA[n:0] | Trace packets            |

|----------------|--------------------------|

| TRACECLT       | Trace Control (optional) |

| TRACECLKOUT    | Trace Clock from Target  |

| TRACECLKIN     | not used                 |

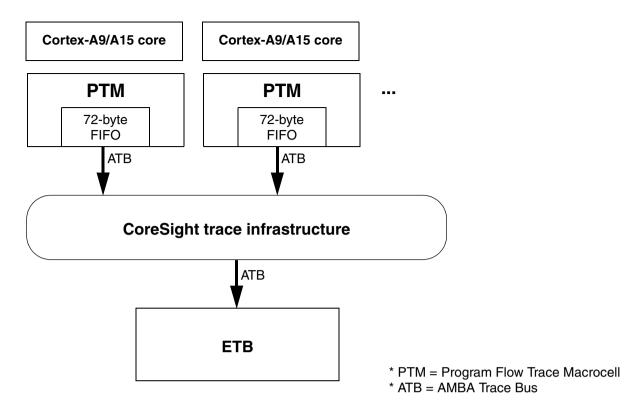

Simplified block diagram for on-chip trace, training-relevant components only:

The PTM generates trace information on certain points in the program (waypoints). TRACE32 needs for a full reconstruction of the program flow also the source code information. Waypoints are:

Indirect branches, with branch destination address and condition code

Direct branches with only the condition code

- Instruction barrier instructions

- Exceptions, with an indication of where the exception occurred

- Changes in processor instruction set state

- Changes in processor security state

- Context ID changes

- Start and stop of the program execution

The PTM can be configured to provide the following additional information:

Cycle count between traced waypoints

- Global system timestamps

- Target addresses for taken direct branches

#### 1. Enable TPIU pins

The TPIU pins need to be enabled, if they are multiplexed with other signals.

PER.Set.simple <address>|<range> [%<format>] <string>

Modify configuration register/onchip peripheral

```

PER.Set SD:0x111D640 %Word 0x9AA0 ; Enable TPIU functionality on PER.Set SD:0x111D6A4 %Word 0x2901 ; GPIO's

PER.Set 0x111600D %Long %LE 0x01E ; Enable CLK

```

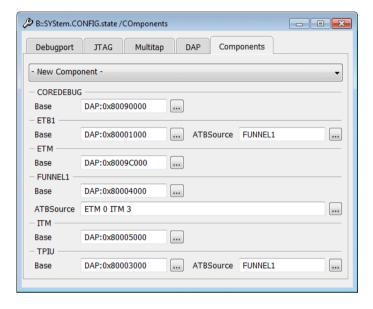

The CoreSight trace infrastructure is automatically configured by TRACE32 PowerView if your chip and its infrastructure is known. Otherwise please contact your local TRACE32 support.

#### SYStem.CONFIG.state /COmponents

Check configuration of CoreSight infrastructure

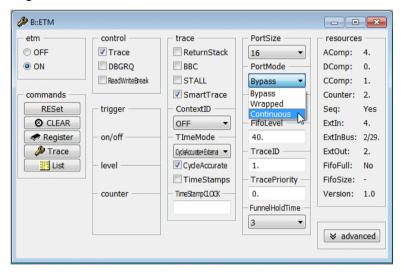

PortSize specifies how many TRACEDATA pins are available on your target to export the trace packets.

ETM.PortSize <size>

ETM.PortMode specifies the Formatter operation mode.

The TPIU/ETB merges the trace information generated by the various trace sources within the multicore chip to a single trace data stream. A trace source ID (e.g ETM.TraceID, ITM.TraceID, HTM.TraceID) allows to maintain the assignment between trace information and its generating trace source. The task of the Formatter within the TPIU/ETB is to embed the trace source ID within the trace information to create this single trace stream.

| Bypass     | There is only one trace source, so no trace source IDs is needed. In this operation mode the trace port interface needs to provide the TRACECTL signal.                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wrapped    | The Formatter embeds the trace source IDs. The TRACECLT signal is used to indicate valid trace information.                                                                                                               |

| Continuous | The Formatter embeds the trace source IDs. Idles are generated to indicate invalid trace information. The TRACE32 preprocessor filters these idles in order to record only valid trace information into the trace memory. |

ETM.PortMode Bypass | Wrapped | Continuous

Push the AutoFocus button to set up the recording tool.

If the calibration is performed successfully, the following message is displayed:

The following setting may be of interest. They are explained in detail later in this training:

ETM.ReturnStack [ON | OFF]

May help to reduce the amount of generated

trace information.

ETM.ContextID 8 | 16 | 32 | OFF

Is required for OS-aware tracing

ETM.TImeMode < mode>

ETM.CycleAccurate [ON | OFF]

ETM.TimeStamps [ON | OFF]

ETM.TimeStampCLOCK <frequency>

Is required for OS-aware tracing

Enable cycle-accurate tracing

Enable global timestamp

Specify clock of global timestamp

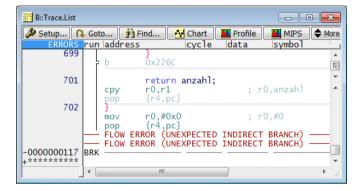

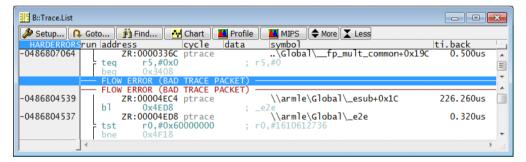

**FLOWERROR:** The trace information is not consistent with the code image in the target memory. This can happen when the code in the target memory was changed or the trace information was corrupted e.g. because of crosstalk on the external trace pins.

**HARDERROR:** The trace port pins are in an invalid state.

This happens if the trace information was corrupted e.g. because of crosstalk on the external trace pins. In rare cases this can be caused by a bug in the chip.

TRACE32 normally uploads only those records from the physical trace memory to the host, that are required by the current trace display/analysis window. To upload the complete trace contents to the host for diagnosis, the following commands are recommended:

#### Trace.FLOWPROCESS

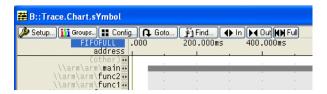

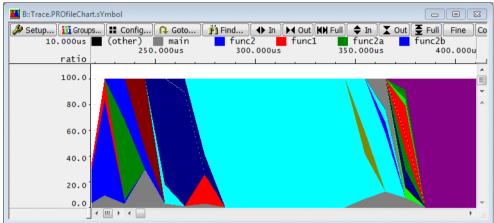

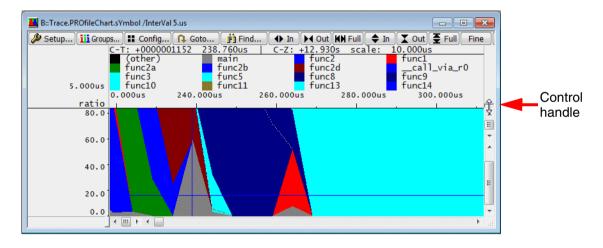

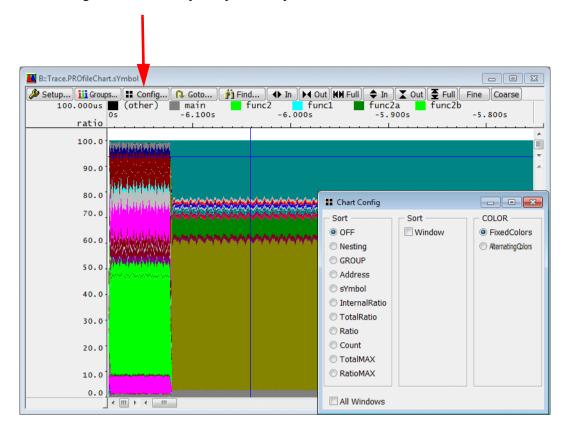

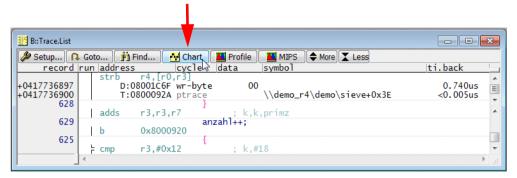

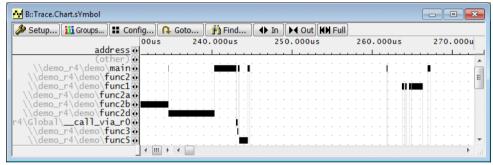

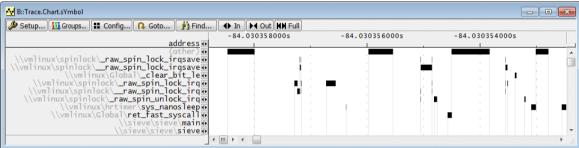

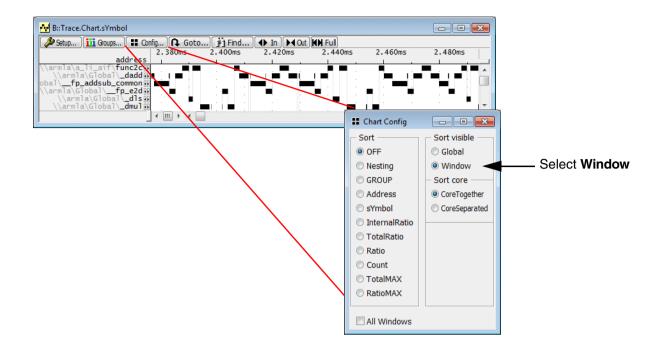

### Trace.Chart.sYmbol

To check the number of FLOWERRORS in the trace use the following command:

PRINT %Decimal Trace.FLOW.ERRORS()

If the trace contains FLOWERRORS / HARDERRORS, please try to set up a proper trace recording before you start to evaluate or analyse the trace contents. See also the section "Diagnosis" in "ARM-ETM Trace" (trace\_arm\_etm.pdf).

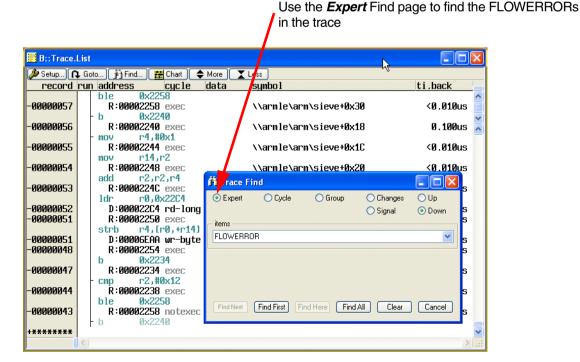

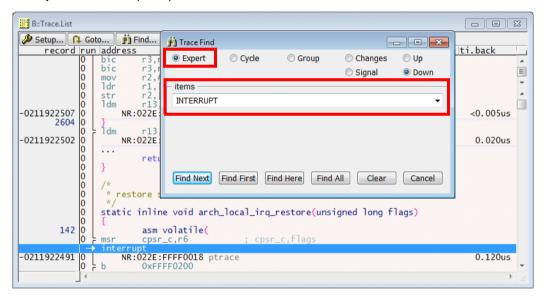

To find the FLOWERRORS / HARDERRORS in the trace use the keyword FLOWERROR in the *Trace.Find* window.

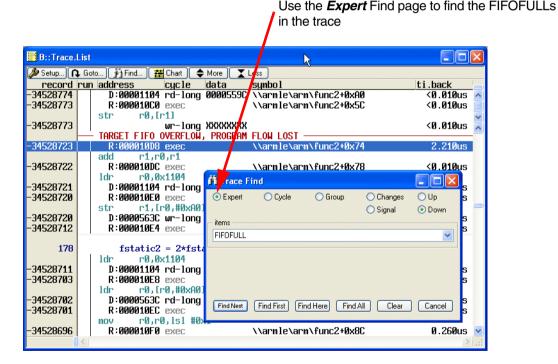

To check the number of FIFOFULLs in the trace use the following command:

PRINT %Decimal Trace.FLOW.FIFOFULL()

To find the FIFOFULLs in the trace use the keyword FIFOFULL in the *Trace.Find* window.

## Source for the Recorded Trace Information

If TRACE32 is started when a PowerTrace hardware and an ETM preprocessor is connected, the source for the trace information is the so-called **Analyzer** (**Trace.METHOD Analyzer**).

The setting Trace.METHOD Analyzer has the following impacts:

1. Trace is an alias for Analyzer.

```

Trace.List ; Trace.List means ; Analyzer.List

Trace.Mode Fifo ; Trace.Mode Fifo means ; Analyzer.Mode Fifo

```

2. All commands from the Trace menu apply to the Analyzer.

3. All Trace commands from the Perf menu apply to Analyzer.

4. TRACE32 is advised to use the trace information recorded to the Analyzer as source for the trace evaluations of the following command groups:

This ETM Training uses always the command group **Trace**. If you are using a CombiProbe or the on-chip ETB as source of the trace information, just select the appropriate trace method and most features will work as demonstrated for the trace method Analyzer.

```

Trace.METHOD CAnalyzer ; select the CombiProbe as source ; for the trace information

Trace.METHOD Onchip ; select the ETB as source for the ; trace information

```

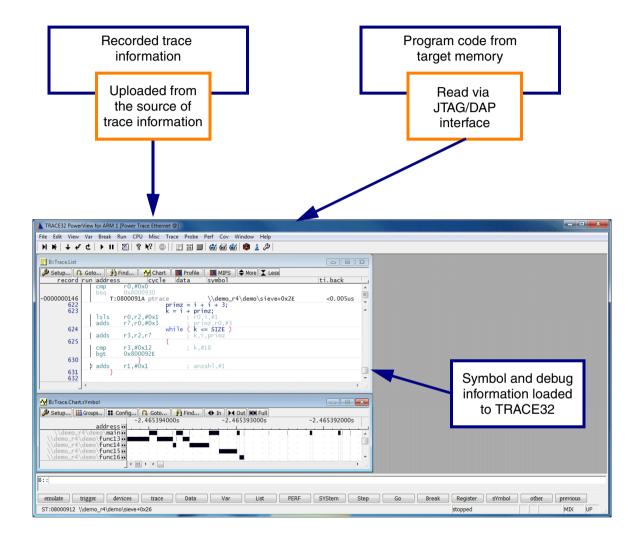

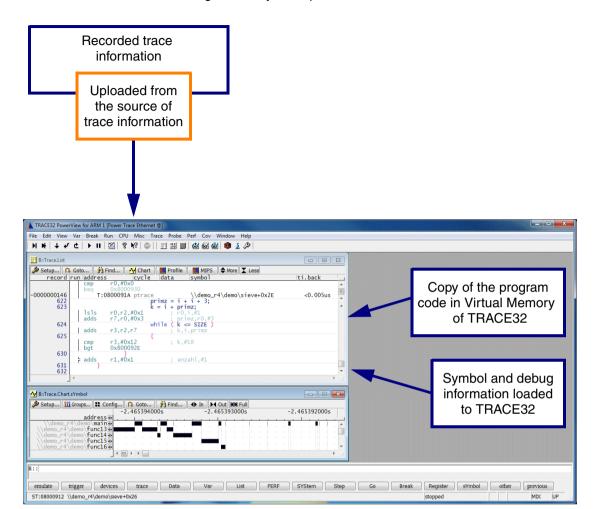

# **Sources of Information for the Trace Display**

In order to provide an intuitive trace display the following sources of information are merged:

- The trace information recorded.

- The program code from the target memory read via the JTAG/DAP interface.

- The symbol and debug information already loaded to TRACE32.

# **Influencing Factors on the Trace Information**

The main influencing factor on the trace information is the ETM itself. It specifies what type of trace information is generated for the user.

Another important influencing factor are the settings in the TRACE32 Trace configuration window. They specify how much trace information can be recorded and when the trace recording is stopped.

An ETM can provide the following trace information:

- Program: Instruction flow mainly based on the target addresses of taken indirect branches

- **Non-Branch Conditionals:** The ARM instruction sets allow also non-branch instruction to be conditional. The trace can contain information if the condition of every conditional instruction has been met or only if the condition of the branch instructions have been met.

- Data Address: The address to/from a data access is writing/reading data-

- Data Value: The data value loaded/stored by a read/write operation

- Context ID: Values of Context ID changes, mainly used to indicate task/process changes and changes of the virtual address space

- Cycle-count (CC): Number of clock cycles between executed instructions

The table below shows what trace information is generated by the various ARM Cortex cores.

| Core                                   | ETM<br>Version       | Program<br>Flow | non-branch<br>conditionals | Data<br>Address | Data<br>Value | Context<br>ID | Cycle<br>Count | bits per instruction |

|----------------------------------------|----------------------|-----------------|----------------------------|-----------------|---------------|---------------|----------------|----------------------|

| ARM7<br>ARM9                           | ETMv1                |                 |                            |                 |               | ≥ ETMv1.2     |                | ≥ 8.00               |

| ARM9                                   | CoreSight<br>ETMv3   |                 |                            |                 |               |               |                | ~1.20                |

| ARM11                                  | (CoreSight)<br>ETMv3 |                 |                            |                 |               |               |                | ~1.20                |

| Cortex-M3/M4<br>Cortex-M23             | CoreSight<br>ETMv3   |                 |                            | (DWT)           | (DWT)         | -             | -              | ~1.20                |

| Cortex-M7<br>Cortex-M33                | ETMv4<br>(Cfg. 3)    |                 |                            | (DWT)           | (DWT)         | -             |                | ~0.35                |

| Cortex-R4<br>Cortex-R5                 | CoreSight<br>ETMv3   |                 |                            |                 |               |               |                | ~1.20                |

| Cortex-R7/R8<br>Cortex-R52             | ETMv4<br>(Cfg. 1)    |                 |                            |                 |               |               |                | ~0.40                |

| Cortex-A5<br>Cortex-A7                 | CoreSight<br>ETMv3   |                 |                            | •               |               |               |                | ~1.20                |

| Cortex-A8                              | CoreSight<br>ETMv3   |                 |                            |                 | -             |               |                | ~1.20                |

| Cortex-A9<br>Cortex-A15<br>Cortex-A17  | PTM                  |                 | -                          | -               | -             | •             | •              | ~0.30                |

| Cortex-A3x<br>Cortex-A5x<br>Cortex-A7x | ETMv4<br>(Cfg. 2)    |                 | -                          | -               | -             |               |                | ~0.30                |

The column "Bits per Instruction" is base on values stated by ARM for program traces without data address/value trace, without conditional non-branch instructions and without cycle-count or internal-timing information (only external tool-base timing).

The ETM can provide also a number of comparators to restrict the generated trace information to the information of interest. They are introduced in detail in the section **Trace Control by Filter and Trigger** of this training.

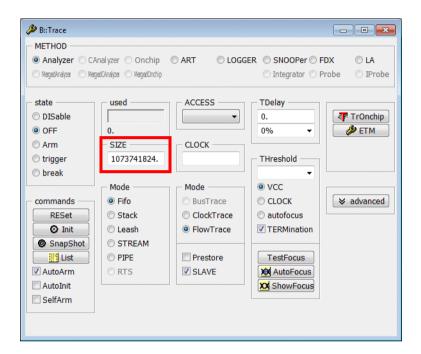

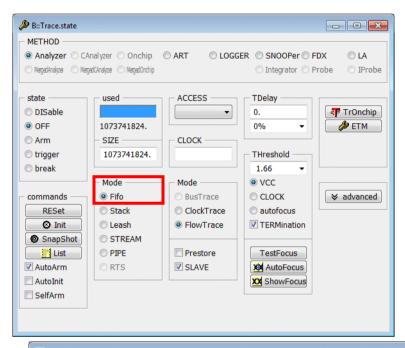

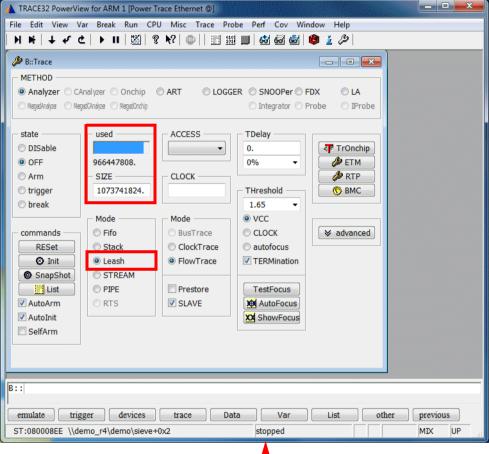

The **Mode** settings in the Trace configuration window specify how much trace information can be recorded and when the trace recording is stopped.

The following modes are provided:

Fifo, Stack, Leash Mode: allow to record as much trace records as indicated in the SIZE field of the Trace configuration window.

- STREAM Mode: STREAM mode specifies that the trace information is immediately streamed to a file on the host computer. Peak loads at the trace port are intercepted by the TRACE32 trace tool, which can be considered as a large FIFO.

- STREAM mode allows a trace memory of several T Frames.

- STREAM mode required 64-bit host computer and a 64-bit TRACE32 executable to handle the large trace record numbers.

- **PIPE Mode:** PIPE mode specifies that the trace information is immediately streamed to the host computer. There it is distributed to a user-defined trace analysis application. This mode is still under construction and will be used mainly for software-generated trace information.

- RTS Mode: The RTS radio button in only an indicator that shows if Real-time Profiling is ON or OFF. For details on Real-time Profiling refer to the RTS command group. RTS is available for ETMv3 and ETMv4.

```

Trace.Mode Fifo ; default mode ; when the trace memory is full ; the newest trace information will ; overwrite the oldest one ; the trace memory contains all ; information generated until the ; program execution stopped

```

```

B::Trace.List

🌽 Setup...] 🔼 Goto... 📑 Find... 🔼 🔥 Chart

Profile

record run address cycle

-0000000190 T:08000920 ptrace

cycle

\\demo_r4\demo\sieve+0x34

625

E

r3,#0x12

; k,#18

CMD

bgt

0x800092E

630

r1,#0x1

- adds

; anzahl,#1

631

632

b

0x800090E

for ( i = 0 ; i <= SIZE ; i++ )

619

adds

r2,#0x1

0x8000908

b

for ( i = 0 ; i <= SIZE ; i++ )

619

r2.#0x12

: i.#18

cmp

-0000000189

BRK

<0.005us

-0000000178

T:08000914 ptrace

\\demo_r4\demo\sieve+0x28

858.185us

1drb

r0,[r0,r2]

```

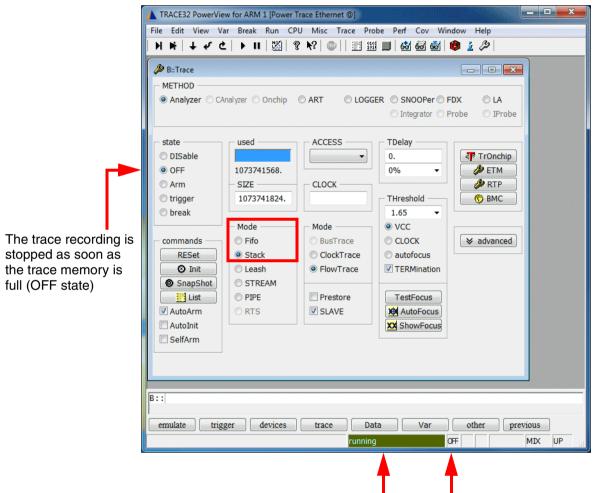

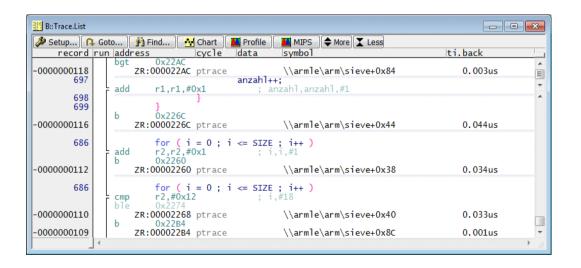

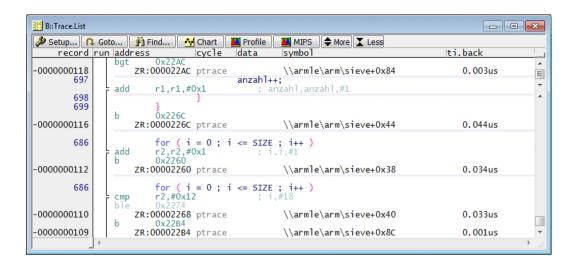

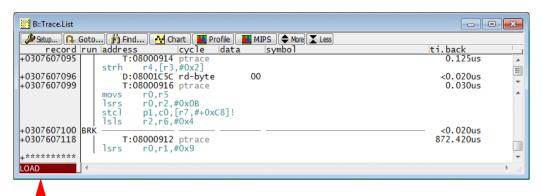

In Fifo mode negative record numbers are used. The last record gets the smallest negative number.

```

Trace.Mode Stack ; when the trace memory is full ; the trace recording is stopped ; the trace memory contains all ; information generated directly ; after the start of the program ; execution

```

Green **running** indicates that the program execution is running,

OFF indicates that the trace recording is switched off

By default, the trace information can not be displayed while the program execution is running. TRACE32 has **NOACESS** to the target memory.

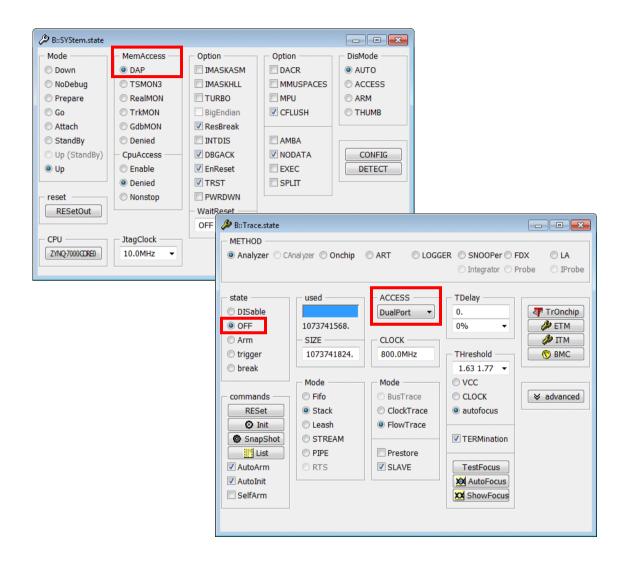

There a three alternative ways to solve the **NOACCESS** issue:

- 1. Stop the program execution. Then TRACE32 has access to the target memory.

- **2. Enable the run-time memory access** (if supported by your chip) and advise TRACE32 to read the target memory via this run-time memory access for trace decoding.

SYStem.MemAccess DAP

Enable run-time memory access.

**Trace.ACCESS DualPort**

Advise TRACE32 to read the target memory via the run-time memory access for trace decoding.

## 3. Provide the program code to TRACE32 via the so-called TRACE32 Virtual Memory.

If there is a copy of the program code in the TRACE32 Virtual Memory TRACE32 reads the code from there, if an access to the target memory is not possible.

- ; load the code from the file demo\_r4.axf to the target and the

- ; TRACE32 Virtual Memory

Data.LOAD.Elf demo\_r4.axf /PlusVM

```

Data.LOAD.Elf demo_r4.axf

; ...

; load the program code to the TRACE32 Virtual Memory

Data.LOAD.Elf demo_r4.axf /VM /NosYmbol /NoClear

```

Caution:

Please make sure that the Virtual Memory of TRACE32 always provides an upto-date version of the program code. Out-of-date program versions will cause FLOW ERRORs.

The trace contents is displayed as soon as TRACE32 has access to the program code.

Since the trace recording starts with the program execution and stops when the trace memory is full, positive record numbers are used in **Stack** mode. The first record in the trace gets the smallest positive number.

```

Trace.Mode Leash ; when the trace memory is nearly ; full the program execution is ; stopped ; Leash mode uses the same record ; numbering scheme as Stack mode

```

The program execution is stopped as soon as the trace buffer is nearly full.

Since stopping the program execution when the trace buffer is nearly full requires some logic/time, **used** is smaller then the maximum **SIZE.**

```

Trace.Mode STREAM ; STREAM the recorded trace ; information to a file on the host ; computer ; (off-chip trace only) ; STREAM mode uses the same record ; numbering scheme as Stack mode

```

The trace information is immediately streamed to a file on the host computer after it was placed into the trace memory. This procedure extends the size of the trace memory to several TFrames.

Streaming mode required 64-bit host computer and a 64-bit TRACE32 executable to handle the large trace record numbers.

By default the streaming file is placed into the TRACE32 temp directory (OS.PresentTemporaryDirectory()).

The command **Trace.STREAMFILE** *<file>* allows to specific a different name and location for the streaming file.

```

Trace.STREAMFILE d:\temp\mystream.t32 ; specify the location for ; your streaming file

```

Please be aware that the streaming file is deleted as soon as you de-select the STREAM mode or when you exit TRACE32.

STREAM mode can only be used if the average data rate at the trace port does not exceed the maximum transmission rate of the host interface in use. Peak loads at the trace port are intercepted by the trace memory, which can be considered to be operating as a large FIFO.

generate very large record numbers

The trace buffer can either sample or allow the read-out for information display.

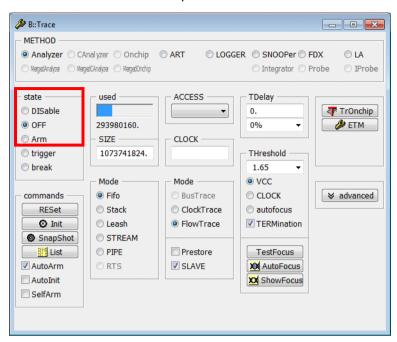

| States of the Trace |                                                                  |

|---------------------|------------------------------------------------------------------|

| DISable             | The trace is disabled.                                           |

| OFF                 | The trace is not recording. The trace contents can be displayed. |

| Arm                 | The trace is recording. The trace contents can not be displayed. |

The Trace states trigger and break are introduced in detail later in this training.

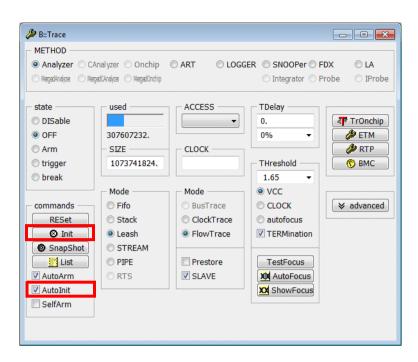

| Init Button       | Delete the trace memory. All other settings in the Trace<br>Configuration window remain valid. |

|-------------------|------------------------------------------------------------------------------------------------|

| AutoInit CheckBox | ON: The trace memory is deleted whenever the program execution is started (Go, Step).          |

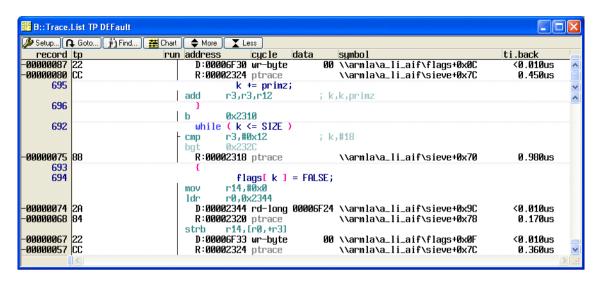

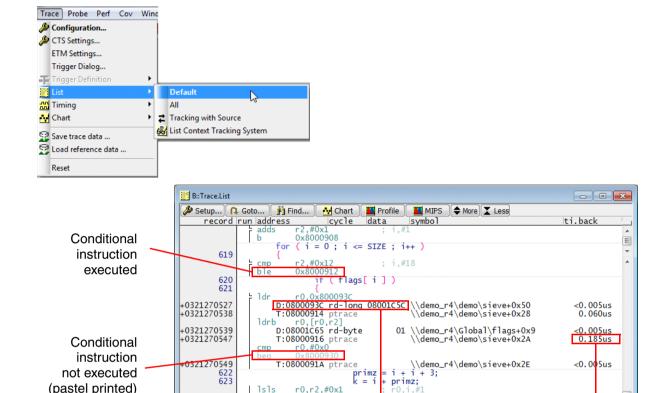

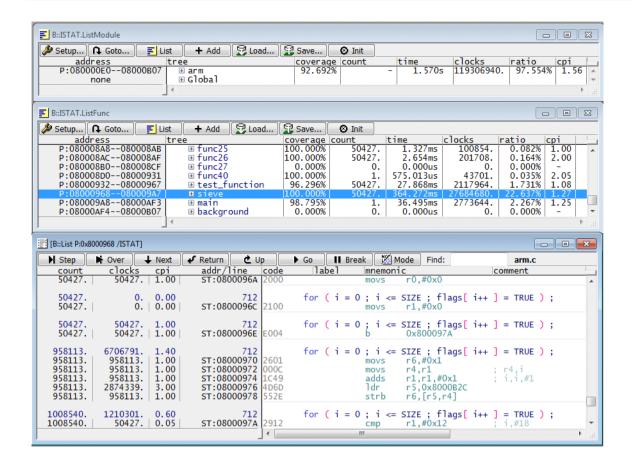

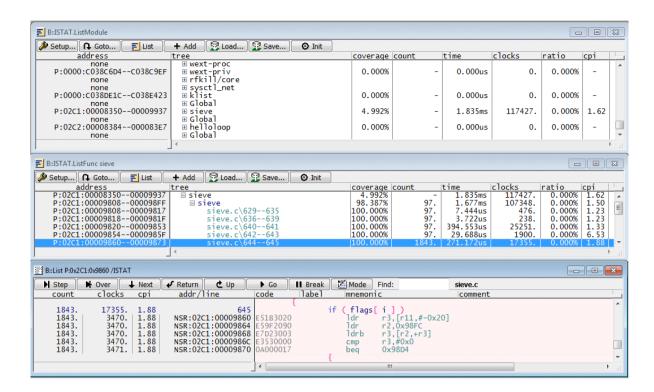

## **Default Listing**

r0,r2,#0x1 r7,r0,#0x3

623

624

lsls adds

k <= SIZE )

while

Timing information

(pastel printed)

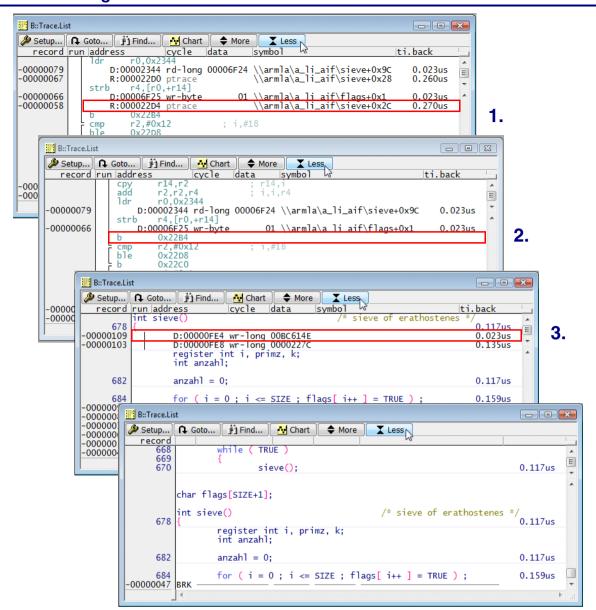

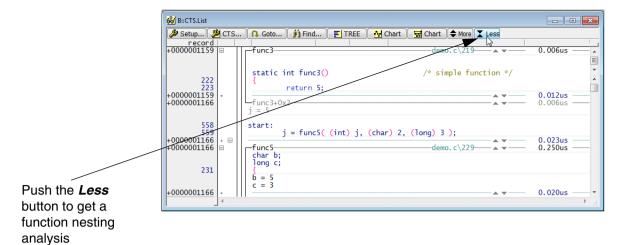

| after pushing 'Less'-button the 1st time | Suppress the display of the program trace package information (ptrace). |

|------------------------------------------|-------------------------------------------------------------------------|

| after pushing 'Less'-button the 2nd time | Suppress the display of the assembly code.                              |

| after pushing 'Less'-button the 3rd time | Suppress the data access information (e.g. wr-long cycles).             |

The *More* button works vice versa.

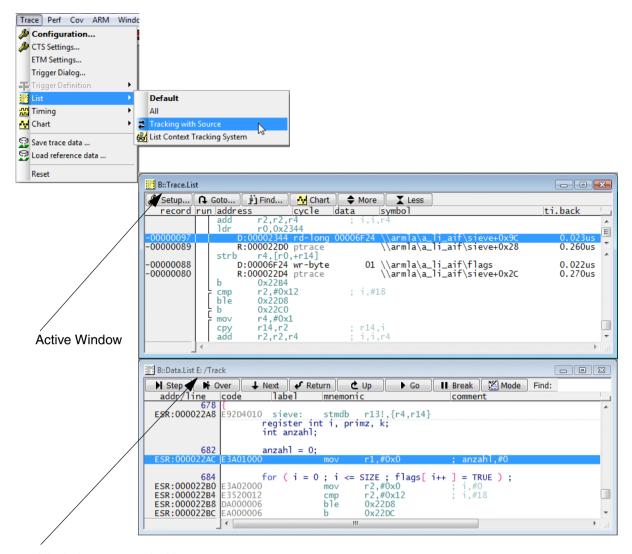

All windows opened with the /*Track* option follow the cursor movements in the active window

| Pg↑         | Scroll page up.                                     |

|-------------|-----------------------------------------------------|

| Pg ↓        | Scroll page down.                                   |

| Ctrl - Pg ↑ | Go to the first record sampled in the trace buffer. |

| Ctrl - Pg ↓ | Go to the last record sampled in the trace buffer.  |

## **Default Display Items**

#### Column record

Displays the record numbers

#### Column run

The column run displays some graphic element to provide a quick overview on the instruction flow.

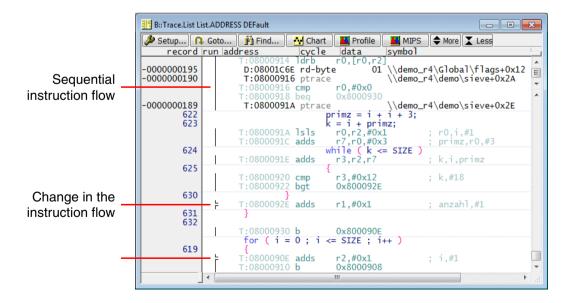

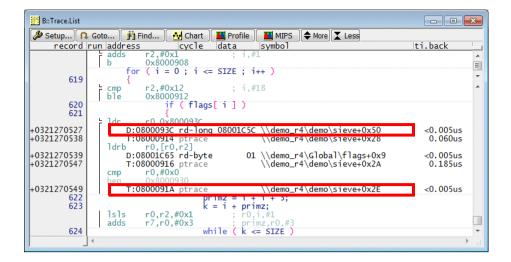

Trace.List List.ADDRESS DEFault

The column run also indicates Interrupts and TRAPs.

```

B::Trace.List

- - X

🤌 Setup...) 📭 Goto... 🏿 👸 Find... 🔂 Chart 🕍 Profile 🗎 MIPS 🕽 🖨 More 🗶 Less

ti.back

record run address

cycle data

NR:0000:FFFF0008 ptrace

-0003153452

0.060us

1dr

pc,0xFFFF0420

NR:0000:C00332C0 ptra

add sp, sp, #S_FRAME_SIZE subs pc, lr, #4

#else

#define A710(code...)

#endif

.align 5

ENTRY(vector_swi)

sub sp, sp, #S_FRAME_SIZE

F sub r13,r13,#0x48

188

```

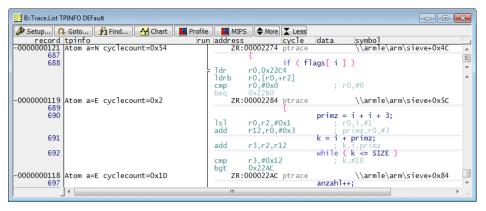

## Column cycle

The main cycle types are:

- ptrace (program trace information)

- rd-byte, rd-word, rd-long (read access)

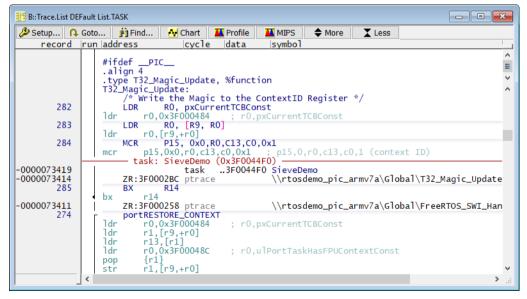

- wr-byte, wr-word, wr-long (write access)

- task (Task ID written via Context ID register)

- overlay (Code-Overlay ID written via Context ID register)

## Column address/symbol

The **address column** shows the following information: <memory\_class>:<logical\_address>

| Memory Classes |                                |

|----------------|--------------------------------|

| Т              | Instruction Thumb mode decoded |

| R              | Instruction ARM mode decoded   |

| D              | Data address                   |

The **symbol column** shows the corresponding symbolic address.

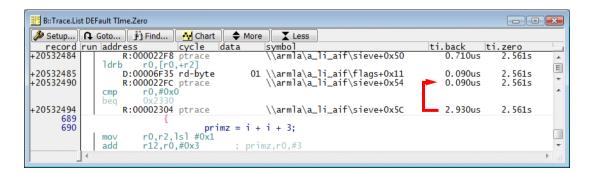

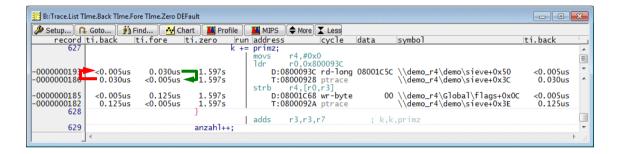

#### Column ti.back

The **ti.back column** shows the time distance to the previous record.

#### **Time Information**

| Time.Back | Time relative to the previous record (red). |

|-----------|---------------------------------------------|

| TIme.Fore | Time relative to the next record (green).   |

| Time.Zero | Time relative to the global zero point.     |

Trace.List TIme.Back TIme.Fore TIme.Zero DEFault

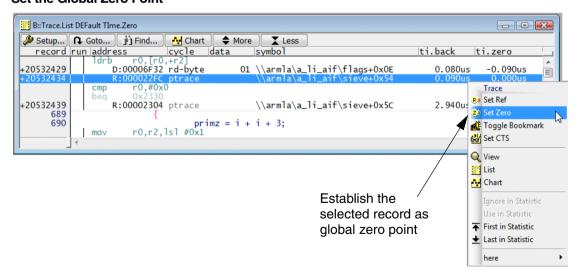

#### Set the Global Zero Point

## **Time Information for Cycle Accurate Mode**

#### Cycle Accurate Mode Pros

Provides accurate core clock cycle information.

Accurate time information can be calculated, if the core clock was constant while recording the trace information.

## Cycle Accurate Mode Cons

Cycle accurate tracing requires up to 4 times more bandwidth.

ETM/PTM trace information can not be correlated with any other trace information.

Trace information has to be processed always from the start of the trace memory. "Tracking" indicates that the display of the trace information might need some time.

## Cycle Accurate Mode and constant core clock while recording

## Example for Cortex-A9:

```

ETM.TImeMode CycleAccurate ; enable cycle accurate mode

Trace.CLOCK 800.MHZ ; inform TRACE32 about your core ; clock frequency

```

## Cycle Accurate Mode and changing core clock while recording

Example for Cortex-A9:

```

; combines cycle accurate mode with \tt TRACE32 global timestamp \tt ETM.TImeMode CycleAccurate+ExternalTrack

```

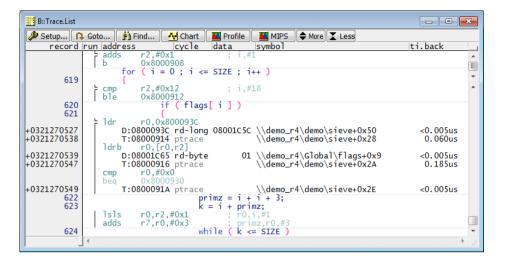

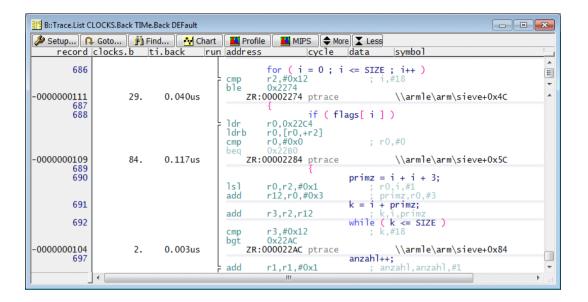

In addition to the timing information the number of clocks needed by an instruction/instructions range can be displayed.

Trace.List CLOCKS.Back TIme.Back DEFault

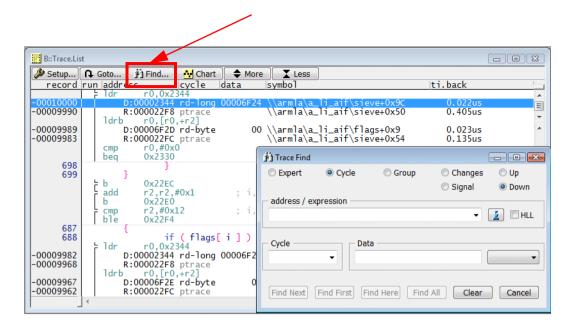

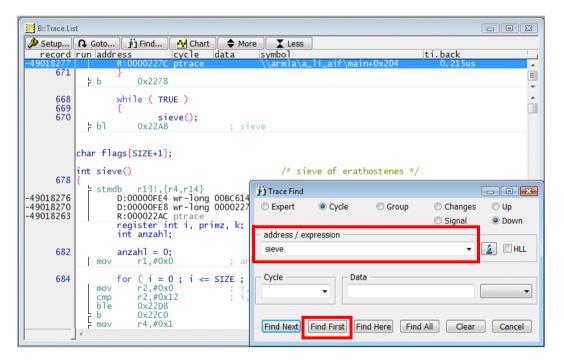

**Example:** Find a specific symbol address.

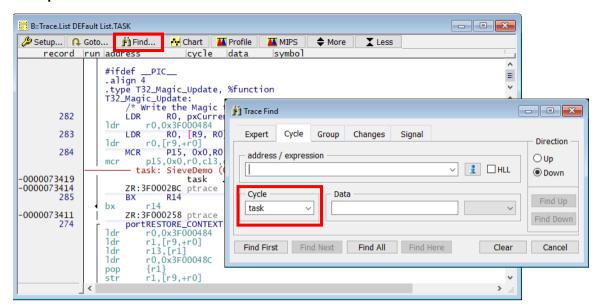

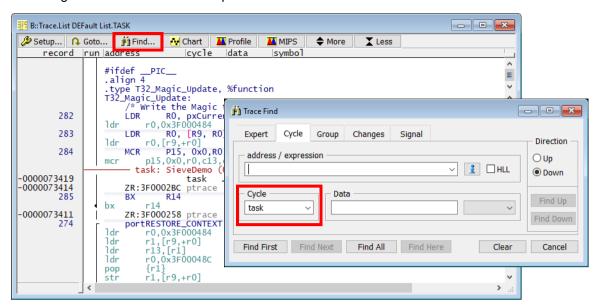

## **Example:** Find Context ID

## Example: Find Interrupt/Trap

# **Belated Trace Analysis**

There are several ways for a belated trace analysis:

- 1. Save a part of the trace contents into an ASCII file and analyze this trace contents by reading.

- 2. Save the trace contents in a compact format into a file. Load the trace contents at a subsequent date into a TRACE32 Instruction Set Simulator and analyze it there.

- 3. Export the ETMv3 byte stream to postprocess it with an external tool.

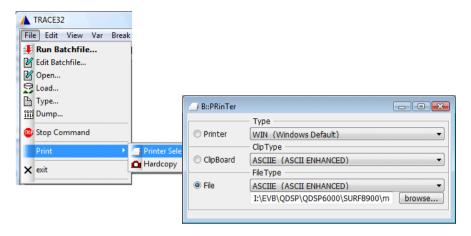

Saving part of the trace contents to an ASCII file requires the following steps:

1. Select **Print** in the **File** menu to specify the file name and the output format.

```

PRinTer.FileType ASCIIE ; specify output format ; here enhanced ASCII

PRinTer.FILE testrun1.lst ; specify the file name

```

2. It only makes sense to save a part of the trace contents into an ASCII-file. Use the record numbers to specify the trace part you are interested in.

TRACE32 provides the command prefix **WinPrint.** to redirect the result of a display command into a file.

```

; save the trace record range (-8976.)--(-2418.) into the ; specified file WinPrint.Trace.List (-8976.)--(-2418.)

```

3. Use an ASCII editor to display the result.

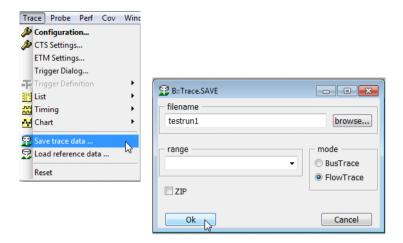

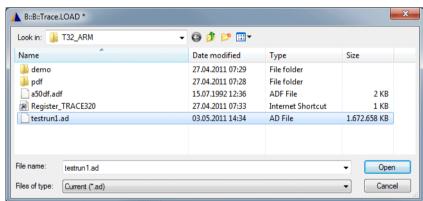

1. Save the contents of the trace memory into a file.

The default extension for the trace file is .ad.

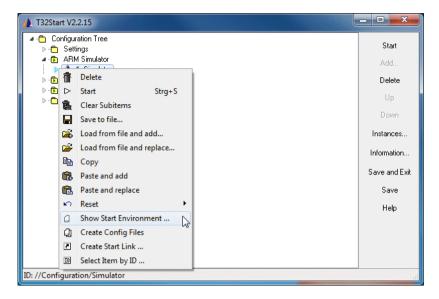

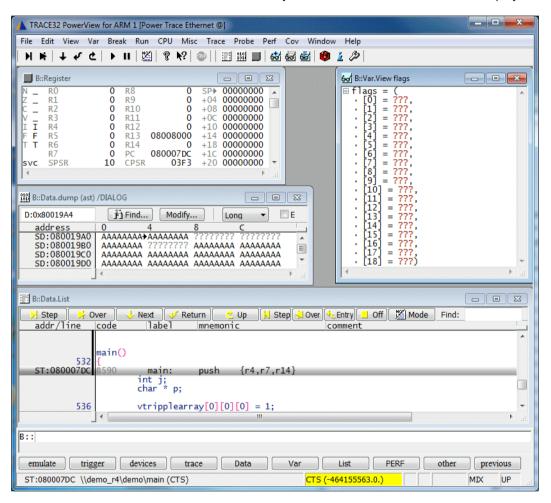

## 2. Start a TRACE32 Instruction Set Simulator (PBI=SIM).

3. Select your target CPU within the simulator. Then establish the communication between TRACE32 and the simulator.

4. Load the trace file.

5. Display the trace contents.

LOAD indicates that the source for the trace information is the loaded file.

6. Load symbol and debug information as you need it.

```

Data.LOAD.Elf demo_r4.axf /NoCODE

```

The TRACE32 Instruction Set Simulator provides the same trace display and analysis commands as the TRACE32 debugger.

## **Export the Trace Information as ETM Byte Stream**

TRACE32 allows to save the ETM byte stream into a file for further analysis by an external tool.

```

Analyzer.EXPORT testrun1.ad /ByteStream

; export only a part of the trace contents

Analyzer.EXPORT testrun2.ad (-3456800.)--(-2389.) /ByteStream

```

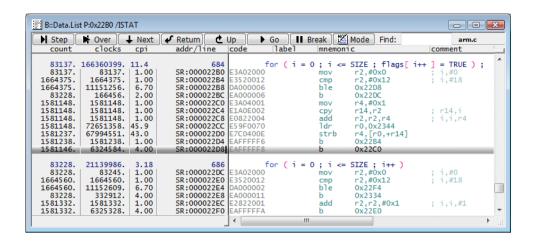

# **Trace-based Debugging (CTS)**

In the past it was necessary to spend a lot of time analyzing the trace listing in order to find out which instructions, data or system states had caused malfunctioning of the target system.

Now Trace-based Debugging - also CTS for Context Tracking System - allows the user to recreate the state of the target system at a selected point based on the information sampled in the trace buffer. From this starting point the program steps previously recorded in real-time in the trace memory can be re-debugged again in the TRACE32 PowerView GUI.

Standard Trace-based Debugging requires:

- Continuous instruction flow trace (Trace.Mode Fifo or Leash)

- Continuous data flow trace (at least read accesses).

If the read data and the operation on the read data are known, the write accesses can be recreated by CTS.

The ARM Cortex core that allow standard Trace-based Debugging are highlighted by a grey background.

| Core                                  | ETM<br>Version       | Program | Data<br>Address | Data<br>Value | Context ID | СС |

|---------------------------------------|----------------------|---------|-----------------|---------------|------------|----|

| ARM7<br>ARM9                          | ETMv1                |         |                 | •             | ≥ ETMv1.2  |    |

| ARM9                                  | CoreSight<br>ETMv3   | •       | •               | •             | •          |    |

| ARM11                                 | (CoreSight)<br>ETMv3 | •       | •               | •             |            |    |

| Cortex-M3 / M4<br>Cortex-M23          | CoreSight<br>ETMv3   |         | (DWT)           | (DWT)         |            |    |

| Cortex-R4<br>Cortex-R5                | CoreSight<br>ETMv3   | •       | •               | •             | •          |    |

| Cortex-R7 / R8<br>Cortex-R52          | CoreSight<br>ETMv4   | •       | •               | •             | •          |    |

| Cortex-A5<br>Cortex-A7                | CoreSight<br>ETMv3   |         |                 | •             |            |    |

| Cortex-A8                             | CoreSight<br>ETMv3   |         |                 |               |            |    |

| Cortex-A9<br>Cortex-A15<br>Cortex-A17 | CoreSight<br>PTM     |         |                 |               |            |    |

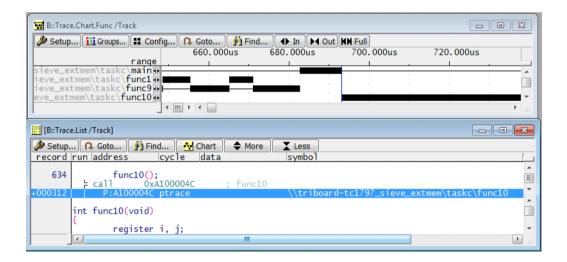

Trace-based Debugging allows to re-debug a trace program section.

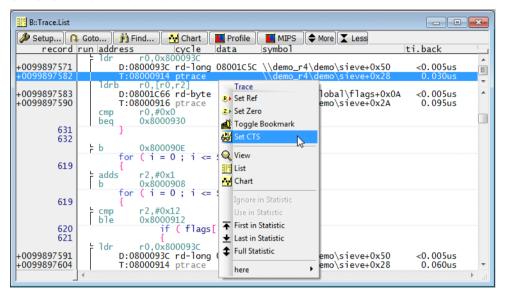

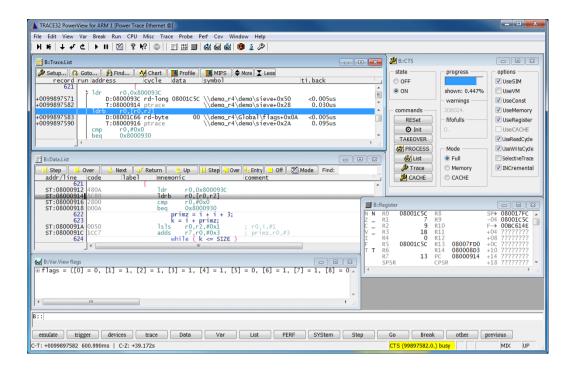

Trace-based Debugging is set up as follows:

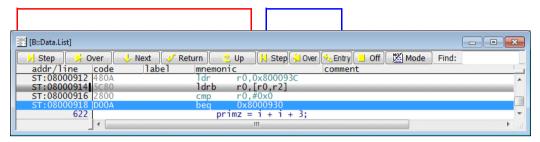

1. Select the trace record that should be the starting point for Trace-based Debugging and select **Set CTS** in the **Trace** context menu.

2. TRACE32 PowerView now recreates the state of the target system as it was when the instruction at the starting point was executed. The recreation take a while (CTS busy).

Please be aware, that CTS recreates the former target state only in the TRACE32 PowerView GUI. This has no effect on the target system.

When CTS is active the TRACE32 PowerView GUI does not show the current state of the target system. It shows a state recreated by the TRACE32 software for the record displayed in the state line.

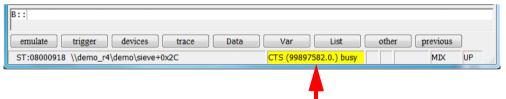

TRACE32 PowerView show the state of the target as it was when the instruction of the trace record 99897582.0 was executed

In order to avoid irritations the look-and-feel of TRACE32 PowerView is changed to yellow when CTS is active.

The main subjects of the CTS recreation are:

- Source listing

- Register contents

- Memory contents

- Call stack and local variables

- Variables

Forward debugging commands

Backward debugging commands

The following **forward debugging** commands can be used to re-debug the traced program section:

- Single step (Step.single)

- Step over call (Step.Over)

- Single step until specified expression changes (Step.Change, Var.Step.Change)

- Single step until specified expression becomes true (Step.Till, Var.Step.Till)

- Go

- Start the program execution. Stop it when the next written instruction is executed (Go.Next)

- Start the program execution and stop it before the last instruction of the current function is executed (Go.Return)

- Start the program execution and stop it after it returned to the calling function (Go.Up)

The following **backward debugging** commands can be used to re-debug the traced program section:

- Step backwards (Step.Back)

- Step backwards over call (Step.BackOver)

- Step backwards until specified expression changes (Step.BackChange, Var.Step.BackChange)

- Step backwards until specified expression becomes true (Step.BackTill, Var.Step.BackTill)

- Run the program backwards (Go.Back)

- Run the program until the start of the current function (Go.BackEntry)

If CTS can not recreate the contents of a memory location or a variable value a ? is displayed.

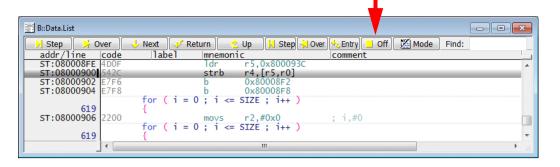

If you want to terminate the re-debugging of a traced program section use the yellow **Off** button (**CTS.OFF**) in the **Data.List** window.

After CTS is switched off the TRACE32 PowerView GUI displays the current contents of your target system.

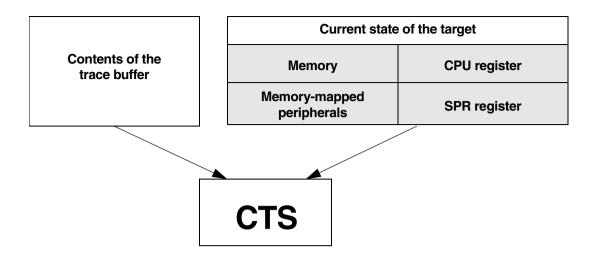

CTS reads and evaluates the current state of the target together with the information recorded to the trace memory:

- 1. CTS can only perform a correct recreation, if solely the core, for which the data trace information is recorded into the trace buffer, writes to memory. If there are memory addresses, e.g. dual-ported memories or peripherals, that are change otherwise, these addresses have to be excluded by the command MAP.VOLATILE from the CTS recreation. These memory addresses are then displayed as unknown (?) if CTS is used.

- CTS performs memory reads while performing a recreation. If read accesses to specific memory-mapped peripherals should be prevented, the addresses have to be excluded by the command MAP.VOLATILE from the CTS recreation. These memory addresses are then displayed as unknown (?) if CTS is used.

- Under certain circumstances the reconstruction of the instruction flow can cause BUSERRORS

on the target system. If this is the case, it is recommended to load the code to TRACE32 Virtual

Memory.

- 4. CTS has to be re-configured if:

- the program execution is still running while CTS is used.

- not all CPU cycles until the stop of the program execution are sampled to the trace.

- the trace contents is reprocessed with a TRACE32 Instruction Set Simulator.

- only the program flow is sampled to the trace buffer.

In all these cases the current state of the target can not be used by CTS. For more information refer to the command CTS.state.

MAP.VOLATILE < range>

Exclude addresses from CTS

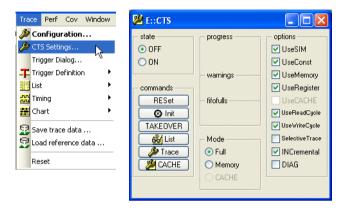

**CTS.state**

Reconfigure CTS.

## **Belated Trace-based Debugging**

The TRACE32 Instruction Set Simulator can be used for a belated Trace-based Debugging. To set up the TRACE32 Instruction Set Simulator for belated Trace-based Debugging proceed as follows:

1. Save the trace information to a file

```

Trace.SAVE my_file

```

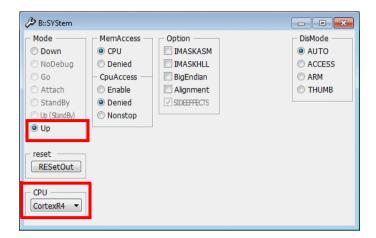

2. Set up the TRACE32 Instruction Set Simulator for a belated Trace-based Debugging:

```

SYStem.CPU CORTEXR4

; select the target CPU

; establish the communication

SYStem.Up

; between TRACE32 and the

; TRACE32 Instruction Set

; Simulator

Trace.LOAD my trace.ad

: load the trace file

Data.LOAD.Elf demo_r4.axf /NoCODE

; load the symbol and debug

; information

Trace.List

; display the trace listing

CTS.UseMemory OFF

; exclude the current memory

: contents from CTS

MAP.CONST 0x8000900++0xff

; inform TRACE32 which memory

; address range provides

; constants

; include constant address

; CTS.UseConst ON

; range into CTS

CTS.UseRegister OFF

; exclude the current register

; contents from CTS

CTS.GOTO -293648539.

; specify the CTS starting

; point

; start the re-debugging

```

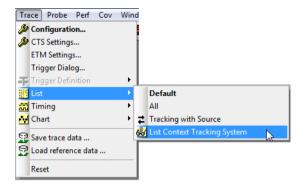

CTS provides also a number of features for high-level language trace display.

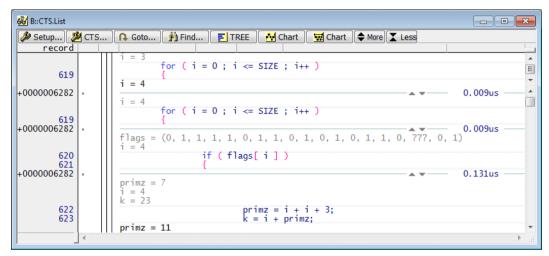

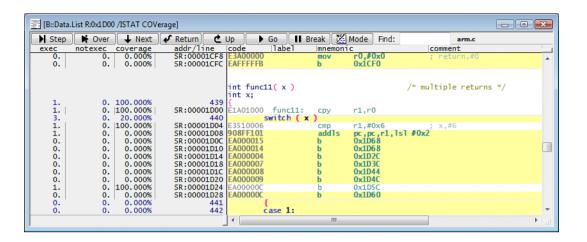

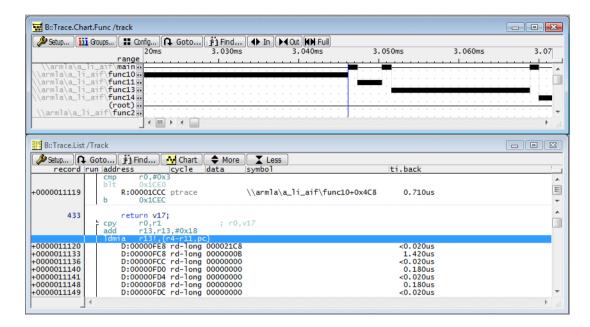

## **Details on each HLL Instruction**

For each HLL step the following information is displayed:

- The values of the local and global variables used in the HLL step

- The result of the HLL step

- The time needed for the HLL step

CTS.List [<record|range>] [<item> ...] [/<option>]

List pure HLL trace.

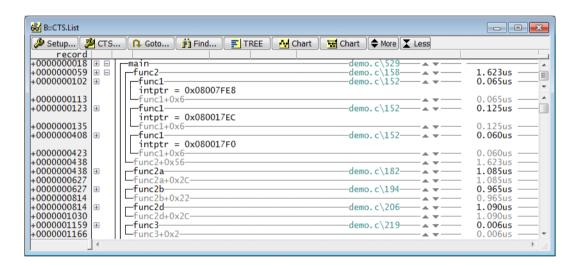

For each function you get the following information:

- Function parameters (and return value not available on all CPUs)

- Time spent in the function

### **Timing Display**

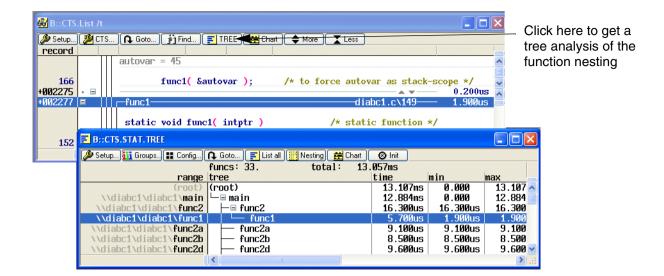

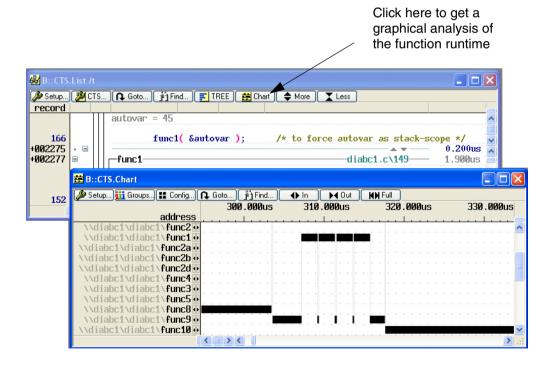

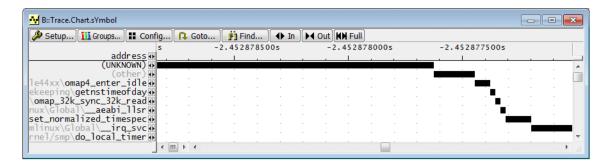

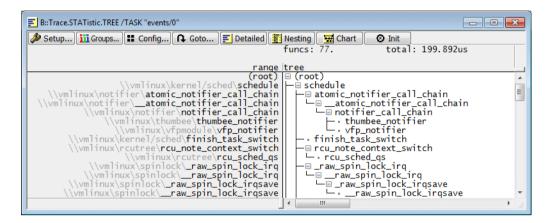

CTS.STATistic.TREE [%<format>][<item> ...] [/<options>]

CTS.Chart.sYmbol [<record\_range>] [<scale>] [/<option>]

Display trace contents as call tree

Display trace contents as timing

based on the symbol information

# **Trace Control by Filter and Trigger**

## **Context**

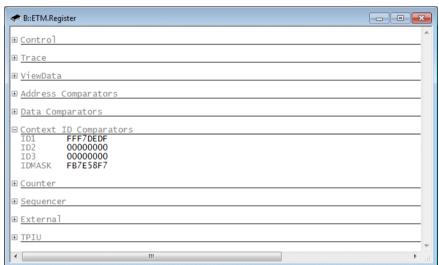

An ETM can contain logic (resources) to control the tracing.

- **Filter:** Address Comparator, Data Comparator and Context ID Comparators are provided to advice the ETM to only generate trace information for events of interest.

- Trigger: Address Comparator, Data Comparator, Context ID Comparators, Counters and a

Three-level Sequencer can be used to send a Trigger to the trace recording. In most cases the

trace recording is stopped when a Trigger occurs.

The table below lists which resources are provided by the various ARM Cortex cores:

| Core                                 | ETM<br>Version       | Address<br>Comparators | Data<br>Comparators | Context ID<br>Comparator | Counters | Sequencer |

|--------------------------------------|----------------------|------------------------|---------------------|--------------------------|----------|-----------|

| ARM7<br>ARM9                         | ETMv1                |                        |                     |                          | •        | •         |

| ARM9                                 | CoreSight<br>ETMv3   |                        |                     | •                        | •        | •         |

| ARM11                                | (CoreSight)<br>ETMv3 |                        |                     |                          |          |           |

| Cortex-M3<br>Cortex-M4<br>Cortex-M23 | CoreSight<br>ETMv3   | (DWT)                  | (DWT)               |                          |          |           |

| Cortex-R4<br>Cortex-R5               | CoreSight<br>ETMv3   |                        |                     | •                        | •        | •         |

| Cortex-R7/R8<br>Cortex-R52           | CoreSight<br>ETMv4   |                        |                     |                          |          |           |

| Cortex-A5<br>Cortex-A7               | CoreSight<br>ETMv3   |                        |                     | •                        |          |           |

| Cortex-A8                            | CoreSight<br>ETMv3   | •                      | •                   |                          |          |           |

| Core                                   | ETM<br>Version     | Address<br>Comparators | Data<br>Comparators | Context ID<br>Comparator | Counters | Sequencer |

|----------------------------------------|--------------------|------------------------|---------------------|--------------------------|----------|-----------|

| Cortex-A9<br>Cortex-A15<br>Cortex-A17  | CoreSight<br>PTM   | •                      |                     | •                        |          | •         |

| Cortex-A3x<br>Cortex-A5x<br>Cortex-A7x | CoreSight<br>ETMv4 |                        |                     |                          | •        | •         |

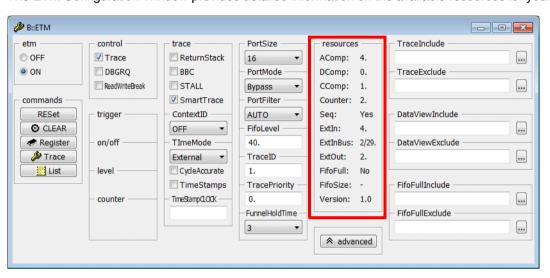

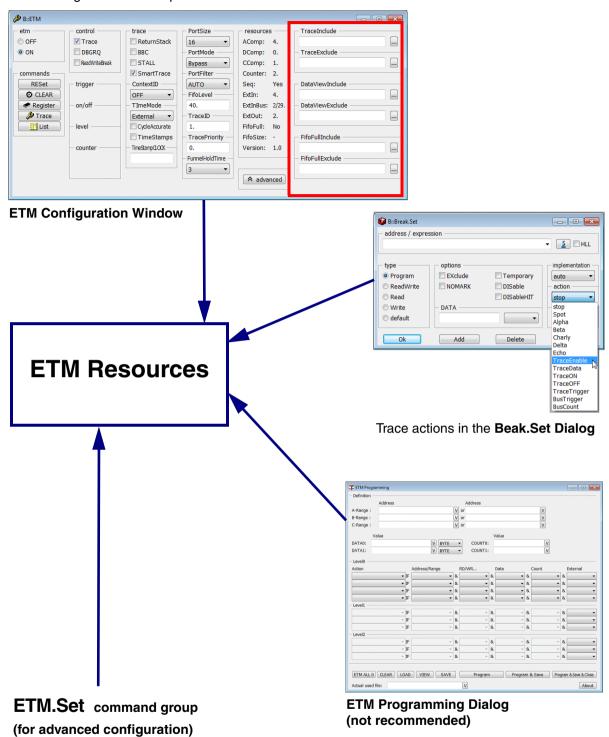

The ETM Configuration Window provides detailed information on the available resources for your core:

| Number of address range comparators                  | AComp    |

|------------------------------------------------------|----------|

| Number of data comparators (single value or bitmask) | DComp    |

| Number of Context ID comparator                      | CComp    |

| Number of 16-bit counters                            | Counter  |

| Three-state sequencer implemented                    | Seq: Yes |

### Special values for "DComp":

- A 0 zero means, you can compare addresses on read/write but you cannot compare data.

- A minus ('-') means, the ETM (or PTM) cannot compare addresses for read/write accesses. (The address comparators can only consider program addresses.)

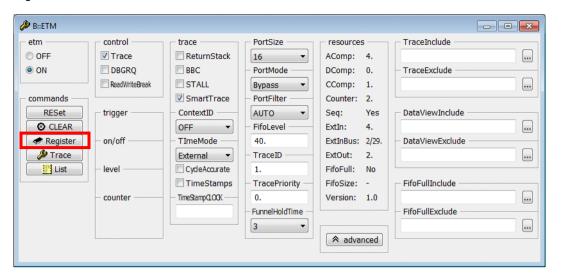

If you push the **Register** button in the ETM Configuration Window, you get a tree display of the control registers for the ETM.

Use the following command, if you want to read the ETM registers while the program execution is running:

ETM.Register , /DualPort

The following TRACE32 components can be used to control the ETM resources.

For advanced configurations via command ETM.Set see "ARM-ETM Trace" (trace\_arm\_etm.pdf)

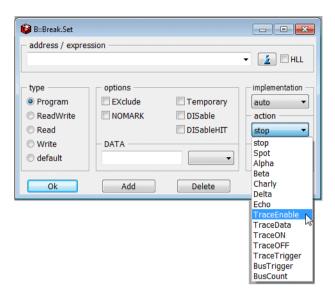

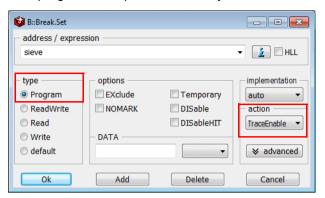

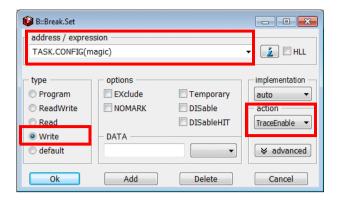

# Filters and Trigger by Using the Break.Set Dialog

| TraceEnable  | Advise the ETM to generate trace information only for the specified data or program event(s).                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TraceData    | Advice the ETM to generate trace information for the complete instruction flow and additionally for the specified data event.                                                             |

| TraceON      | Advise the ETM to start with the generation of trace information at the specified event.                                                                                                  |

| TraceOFF     | Advise the ETM to stop the generation of trace information at the specified event.                                                                                                        |

| TraceTrigger | Advise the ETM to generate a Trigger for the trace recording at the specified event.                                                                                                      |

|              | If the ETM Trigger is not already connected to the TPIU in your CoreSight system, this connection has to be configured manually by the corresponding CTI (Cross Trigger Interface) setup. |

| BusTrigger   | Advise the ETM to generate a pulse at ETM External Output 1 at the specified event.                                                                                                       |

| BusCount     | Advise the ETM to decrement an ETM counter at the specified event.                                                                                                                        |

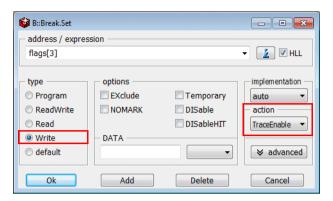

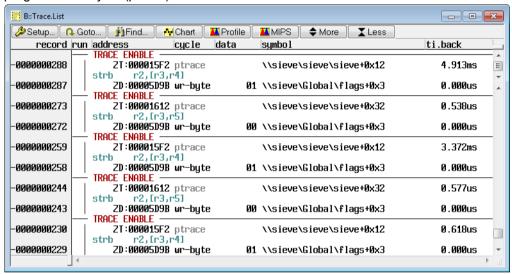

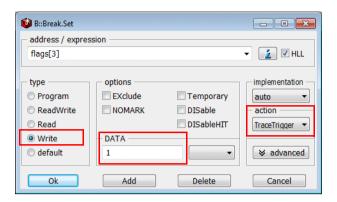

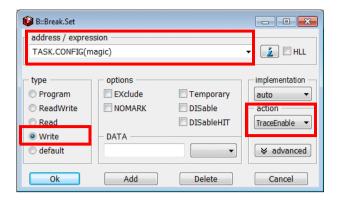

**Example 1:** Advise the ETM to generate only trace information for the write accesses to the variable flags[3].

1. Set a write breakpoint to flags[3] and select the action TraceEnable.

- 2. Start the program execution and stop it.

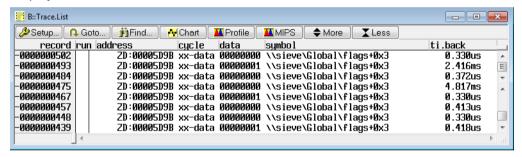

- Display the result.

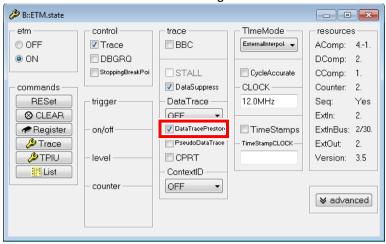

4. If you'd like to have details about the instruction that performed the write access, enable DataTracePrestore in the ETM Configuration Window.

5. With ETM.DataTracePrestore ON you see in Trace.List for every data-cycle also the associated program trace cycle (ptrace):

Using DataTracePrestore generates additional trace data with ETMv3.

With ETMv1 and ETMv4 any data trace cycle is always generated together with a program trace cylce. Thus for ETMv1/v4 DataTracePrestore just controls if the debugger *displays* the program trace cylce.

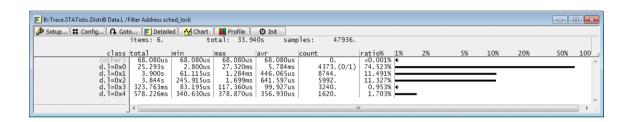

**Example 2:** Advise the ETM to generate only trace information for the write accesses to the variable sched lock. Perform various statistical analysis on the trace contents.

```

; advise the ETM to only generate trace information for the write

; accesses to the variable sched_lock

Var.Break.Set sched_lock /Write /TraceEnable

; start and stop the trace recording to fill the trace memory

Go

...

Break

; display the trace memory contents

Trace.List

; analyse the contents of the variable sched_lock statistically

Trace.STATistic.DistriB Data.L /Filter Address sched_lock

```

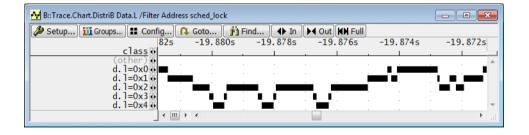

; display a timing diagram that illustrates the contents changes of ; the variable sched\_lock

Trace.Chart.DistriB Data.L /Filter Address sched\_lock

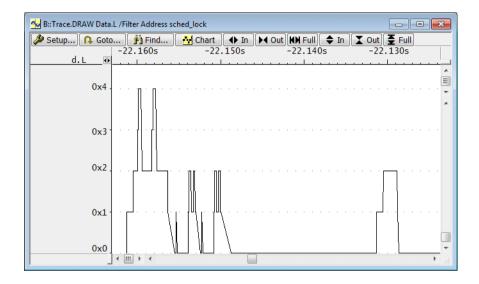

// display a graph over time of the variable "sched\_lock"

#### Trace.DRAW.Var %DEFault sched lock

// or

Trace.DRAW.channel Data.L /Filter Address sched\_lock

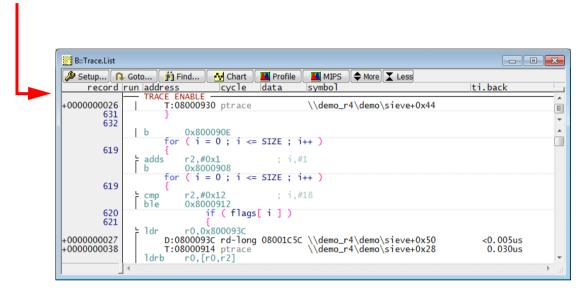

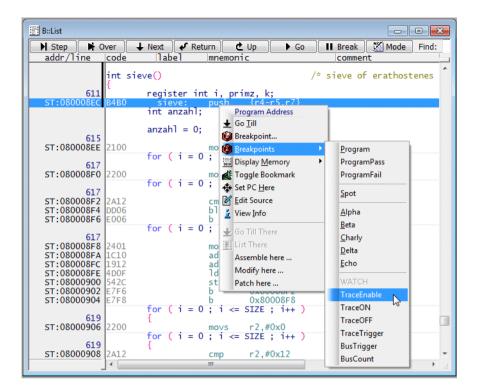

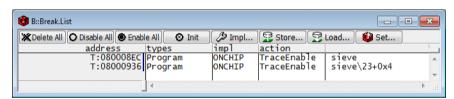

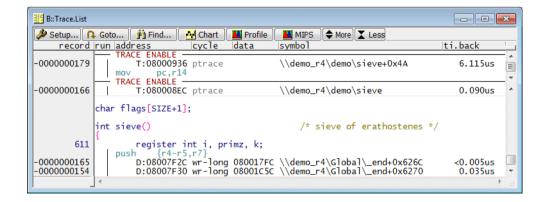

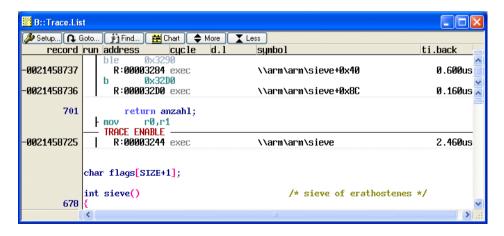

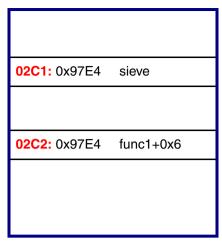

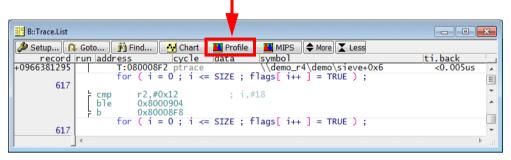

**Example 1:** Advise the ETM to generate trace information only for the entry to the function sieve.

1. Set a program breakpoint to the entry of the function sieve and select the action TraceEnable.

- 2. Start the program execution and stop it.

- Display the result.

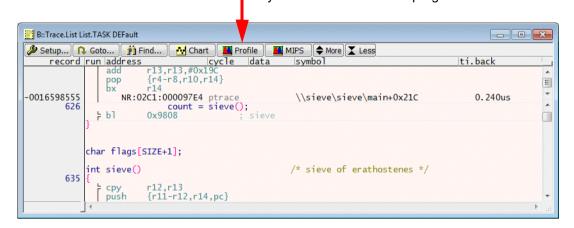

```

B::Trace.List

🤌 Setup... 🔼 Goto... 📫 Find... 🚹 Chart 📕 Profile 📕 MIPS 🗘 More 🗶 Less

record run address

ti.back

cycle data

TRACE ENABLE

-0000000147

ZR:00002228 ptrace

8.900us

\\armle\arm\sieve

char flags[SIZE+1];

/* sieve of erathostenes */

int sieve()

678

push

{r4,r14}

register int i, primz, k;

int anzahl;

anzah1 = 0;

682

; anzah1,#0

mov

r1,#0x0

684

for (i = 0; i \leftarrow SIZE; flags[i++] = TRUE);

; i,#0

for ( i = 0 ; i <= SIZE ; flags[ i++ ] = TRUE ) ; \stackrel{?}{1}, \#0x12

684

0x2258

TRACE ENABLE

0000000138

ZR:00002228 ptrace

\\armle\arm\sieve

8.860us

```

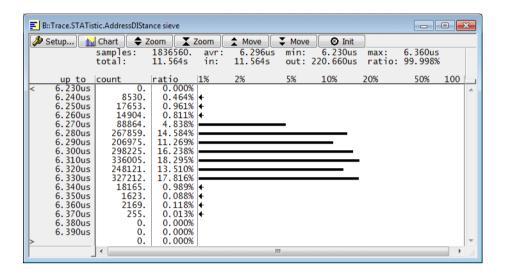

Use the following command, if you want to perform a statistical evaluation of this event.

Trace.STATistic.AddressDIStance sieve

#### For ARM Cortex CPUs:

When measuring execution times while only parts of the program flow have been traced (by using trace filters TraceEnable, TraceON or TraceOFF) **you should not use external (tool based) time stamps**. On ARM Cortex CPUs already generated trace packets might not leave your chip when the trace filter disables the ETM/PTM. The packets are then recorded when the ETM/PTM gets re-enabled, which gives wrong external timestamps.

Best is to use ETM.TlmeMode CycleAccurate, when using trace-filters.

Alternatively you can use ETM.TlmeMode SyncTimeStamps or ETM.TlmeMode AsyncTimeStamps (if an internal chip-internal time stamper is available)

See command **ETM.TimeMode** in "**ARM-ETM Trace**" (trace\_arm\_etm.pdf) for more details.

If you use external (tool based) time stamps (**ETM.TImeMode External**) to measure execution times while only parts of the program flow have been traced (by using trace filters TraceEnable, TraceON or TraceOFF), ensure that the port-filter of you trace preprocessor (or CombiProbe or  $\mu$ Trace) is set to ON. (**Trace.PortFilter ON**) Otherwise trace packets might be highly delayed in your trace tool.

**Example 2:** Advise the ETM to generate trace information for the entries and exits to the function sieve.

Mark the entry and the exit of the function sieve with an TraceEnable breakpoint.

- 2. Start the program execution and stop it.

- Display the result.

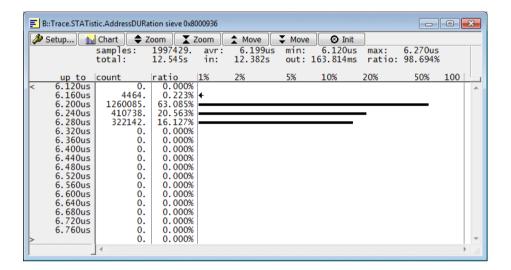

Use the following command, if you want to get a statistical analysis of the time spent between the entry and exits of the function sieve. (The function sYmbol.EXIT(<func>) returns the exit address of a function.)

Trace.STATistic.AddressDURation sieve sYmbol.EXIT(sieve)

#### For ARM Cortex CPUs:

When measuring execution times while only parts of the program flow have been traced (by using trace filters TraceEnable, TraceON or TraceOFF) **you should not use external (tool based) time stamps**. On ARM Cortex CPUs already generated trace packets might not leave your chip when the trace filter disables the ETM/PTM. The packets are then recorded when the ETM/PTM gets re-enabled, which gives wrong external timestamps.

Best is to use ETM.TlmeMode CycleAccurate, when using trace-filters. Alternatively you can use ETM.TlmeMode SyncTimeStamps or ETM.TlmeMode AsyncTimeStamps (if an internal chip-internal time stamper is available)

See command **ETM.TimeMode** in "**ARM-ETM Trace**" (trace\_arm\_etm.pdf) for more details.

If you use external (tool based) time stamps (**ETM.TImeMode External**) to measure execution times while only parts of the program flow have been traced (by using trace filters TraceEnable, TraceON or TraceOFF), ensure that the port-filter of you trace preprocessor (or CombiProbe or  $\mu$ Trace) is set to ON. (**Trace.PortFilter ON**) Otherwise trace packets might be highly delayed in your trace tool.

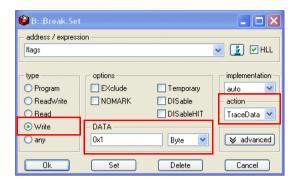

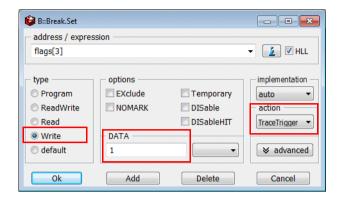

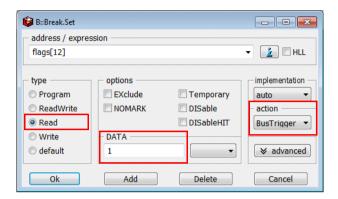

**Example:** Advise the ETM to generate trace information for the complete instruction flow and for the write accesses where 1 is written as a byte to the variable flags.

1. Set a Write breakpoint to the HLL variable flags, define DATA 1 and select the action TraceData.

- 2. Start the program execution and stop it.

- Display the result.

**Example:** Sample only the function sieve.

1. Set a Program breakpoint to the entry of the function sieve and select the action TraceON.

2. Set a Program breakpoint to the exit of the function sieve and select the action TraceOFF.

- 3. Start the program execution and stop it.

- 4. Display the result.

The ETM stops the generation for the trace information before trace information is generated for the event the causes the stop.

**Example:** Stop the recording to the trace buffer after 1 was written to flags[3].

Set a write breakpoint to flags[3], define DATA 1 and select the action TraceTrigger.

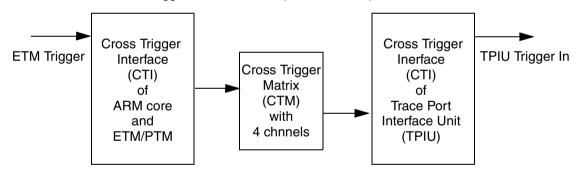

2. Establish the connection between the ETM Trigger and the TPIU via the Cross Trigger Interface (CTI) if required.

This is only required for chips with ETMv3 or PTM and CoreSight debug infrastructure (Cortex-R4/R5 and Cortex-A5 to A17). You can skip this step for Cortex-M and cores with ETMv4 (with ETMv4 the trigger is propagated via the trace bus (ATB).)

You have to set up both the Cross Trigger Interface (CTI) of you trigger-source - here the ETM/PTM - and the sink for the trace trigger - here the TPIU (or ETF or ETR).

```

; core specific example

; configure ETM trigger to channel 3

; enable Core/ETM CTI

Data.Set APB:0x80001000 %Long 1

; map CTITRIGIN[6] (ETM Trigger Out) to channel 3

Data.Set APB:0x80001038 %Long Data.Long(APB:0x80001038) | 0x4

; configure channel 3 to TPIU Trigger In

; enable System/TPIU CTI

Data.Set APB:0x80002000 %Long 1

; Map channel 3 to CTITRIGOUT[3] (TPIU Trigger In)

Data.Set APB:0x800020AC %Long Data.Long(APB:0x800020AC) | 0x4

```

The peripheral file "percti.per" in your TRACE32 system folder can help you to configure the CTIs:

```

DO "~~/percti.per" <cti_base_address>

```

Check your chips data sheet, for the base addresses of the CTI interface for both ETM and TPIU (or ETF or ETR).

The following CTI inputs and outputs are use by the different ARM cores:

| ARM core     | ETM Trigger Output to CTM Channel | Core Break Input from CTM Channel | Core Halt Output to CTM Channel |  |  |  |

|--------------|-----------------------------------|-----------------------------------|---------------------------------|--|--|--|

| ARM9 / ARM11 | CTITRIGIN[6]                      | CTITRIGOUT[0]                     | CTITRIGIN[0]                    |  |  |  |

| Cortex-R4    | CTITRIGIN[6]                      | CTITRIGOUT[0]                     | CTITRIGIN[0]                    |  |  |  |

| Cortex-A9    | CTITRIGIN[6]                      | CTITRIGOUT[0]                     | CTITRIGIN[0]                    |  |  |  |

| Cortex-M3    | CTITRIGIN[7]                      | CTITRIGOUT[0]                     | CTITRIGIN[0]                    |  |  |  |

| Cortex-R7    | CTITRIGIN[2]                      | CTITRIGOUT[0]                     | CTITRIGIN[0]                    |  |  |  |

| ARMv8-A      | CTITRIGIN[4]                      | CTITRIGOUT[0]                     | CTITRIGIN[0]                    |  |  |  |

|              |                                   |                                   |                                 |  |  |  |

| Trace Sink   | Trigger Input from C              | Trigger Input from CTM Channel    |                                 |  |  |  |

| TPIU         | CTITRIGOUT[3]                     |                                   |                                 |  |  |  |

| ETF          | CTITRIGOUT[7]                     |                                   |                                 |  |  |  |

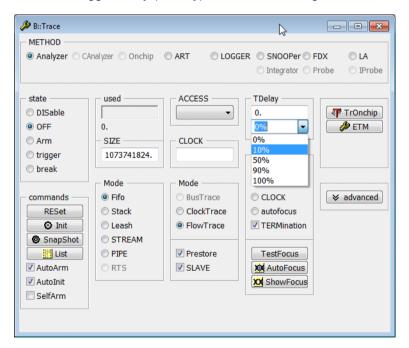

3. Configure an optional delay with **Trace.TDelay** *<time>* | *<ETM cycles>* | *<percent of trace-buffer>* When the trace trigger occurs, the recording will stop after the specified delay.

CTITRIGOUT[1]

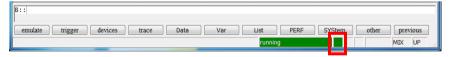

4. Start the program execution.

**ETR**

The Trace State field in the command line is green, as long a the trace recording is active

The Trace State field in the command line becomes **blue** after the trace recording was stopped by the Trigger (BRK)

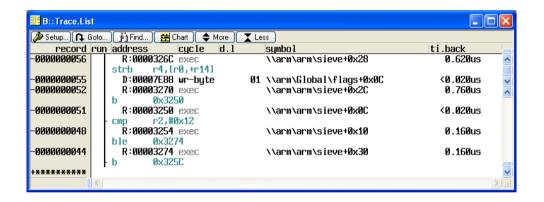

5. Display the result.

Displaying the result requires access to the target memory in order to read the code information. To display the result:

- Stop the program execution or

- Load the code to the TRACE32 Virtual Memory before you use the TraceTrigger action (Data.LOAD <file> /VM).

```

B::Trace.List

| Reduction | Redu

🤌 Setup... 🔼 Goto... 🏿 👸 Find... 🔀 Chart 🖊 🔛 Profile 🖊 🖊 MIPS 🕽 🖨 More 🗶 Less

ti.back

0.370us

E

<0.005us

0.185us

T:080008F2 ptrace \\demo_r4\demo\sieve+ for ( i = 0 ; i <= SIZE ; flags[ i++ ] = TRUE ) ;

<0.005us

617

- p

cmp

ble

r2,#0x12

0x8000904

; i,#18

0x80008F8

for ( i = 0 ; i <= SIZE ; flags[ i++ ] = TRUE ) ;

617

r4,#0x1

r0,r2,#0x0

r2,r2,r4

r5,0x800093C

adds

; r0,i,#0

; i,i,r4

adds

ldr

-0000000017

D:0800093F rd-data

\\demo_r4\demo\sieve+0x53

<0.005us

```

The trace recording is stopped before the event that caused the triggered is exported by the ETM.

**Example:** Stop the sampling to the trace buffer after 1 was written to flags[3] and another 10% of the trace buffer is filled.

1. Set a write breakpoint to flags[3], define DATA 1 and select the action TraceTrigger.

2. Define the trigger delay (TDelay) in the Trace Configuration Window.

3. Start the program execution.

The Trace State field in the command line is green, as long a the trace recording is active

The Trace State field in the command line becomes cyan after the Trigger occured (TRG) and the trigger delay (TDelay) starts

The Trace State field in the command line becomes **blue** after the trace recording was stopped because the trigger delay ran down (BRK)

4. Display the result.

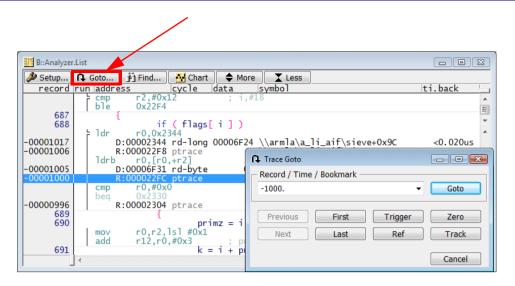

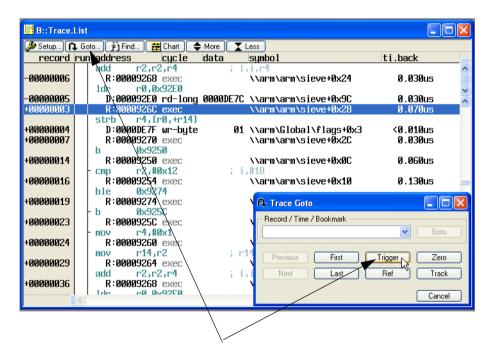

Push the *Trigger* button in the *Trace Goto* window to find the record, where TraceTrigger was accepted by the trace. Here the sign of the record numbers has changed.

Example: Indicate with a pulse on ETM External Output 1 that 0 was read from flags[12].

In order to measure this pulse on ETM External Output 1 you need to check where the ETM External Output 1 can be measured on your core.

1. Set a read breakpoint to flags[12], define DATA 1 and select the action BusTrigger.

2. Measure the result.

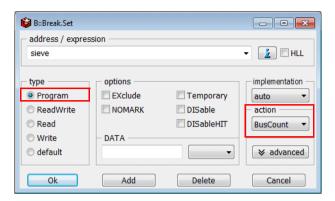

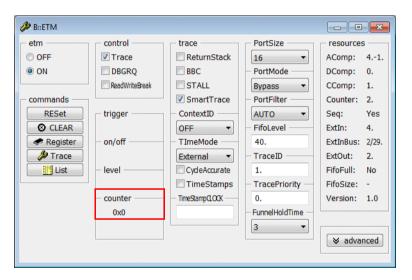

**Example:** Advise the ETM to decrement its counter at each entry to the function sieve.

1. Set a program breakpoint to the entry of the function sieve and select the action BusCount.

2. Use the ETM configuration window to observe the counter.

#### 3. Start the program execution

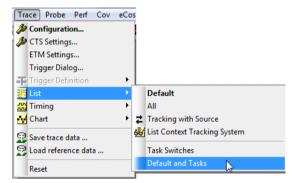

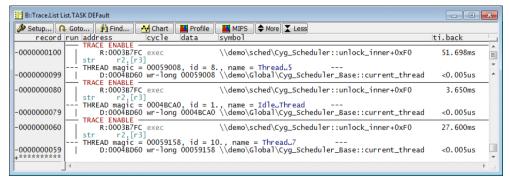

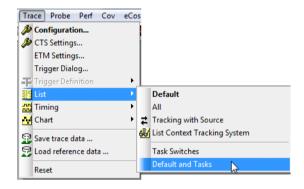

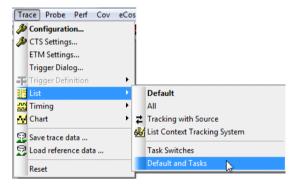

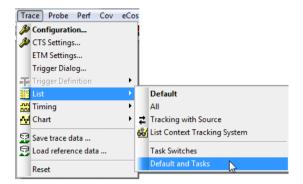

## **OS-Aware Tracing**

OS-aware tracing is relatively simple if you use an operating system that does not use dynamic memory management (e.g. eCos).

The OS-aware tracing for an operating that uses dynamic memory management to handle processes/tasks is more complex. That is why this is explained in a separate chapter.

## **OS (No Dynamic Memory Management)**

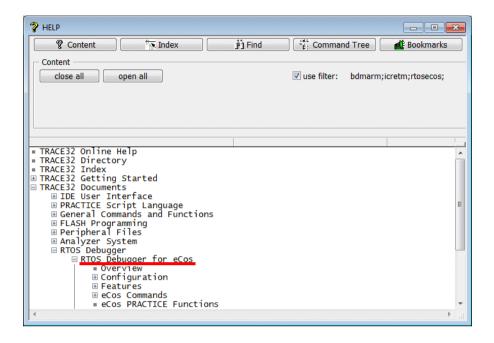

### **Activate the TRACE32 OS Awareness (Supported OS)**

TRACE32 includes a configurable target-OS debugger to provide symbolic debugging of operating systems.

Lauterbach provides configuration files for most common available OS.

If your kernel is compiled with symbol and debug information, the adaptation to your OS can be activated as follows:

TASK.CONFIG <file> Configures the OS debugger using a configuration file provided by

Lauterbach

MENU.ReProgram <file> Program a ready-to-run OS menu

**HELP.FILTER.Add** *<filter>* Add the help information for the OS debugger

All necessary files can be found under  $\sim\sim/\text{demo/arm/kernel}$ , where  $\sim\sim$  expands to the TRACE32 system directory.

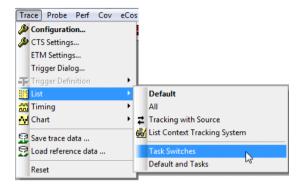

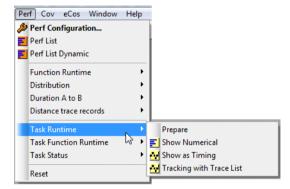

#### **Example for eCos:**