| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

|                            |                   |                                       |                   |                     |

# JTAG Switcher

#### Alexander Merkle - Lauterbach GmbH

18 October 2019

◆□ > ◆□ > ◆ Ξ > ◆ Ξ > → Ξ = の < @

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

| Overview                   |                   |                                       |                   |                     |

## **1** JTAG Daisy-Chaining Basics

## 2 Limitations

## **3** JTAG Switcher

#### Advanced Features

## 5 FPGA Implementation

| Abbreviations              |                   |                                       |                   |                     |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

- TAP: Test-Access-Port, JTAG communication unit, consists of Instruction-& multiple Data-Registers selected by a state-machine

- Daisy-Chain: connection of multiple TAPs via a single interface

- JTAG Signals:

- TCK: Test Clock, clocks all D-flip-flops, which are part of the JTAG architecture

- TMS: Test Machine State, controls the JTAG TAP Controller state machine

- TDI: Test Data In, serial data send into the JTAG architecture

- TDO: Test Data Out, serial data received from the JTAG architecture

- TRST\*: Test Reset, optional, will *asynchronously* reset the JTAG TAP Controller state machine, putting it into the "Test-Logic-Reset" state

| JTAG Daisy-Chaining Basics<br>●00000 | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|--------------------------------------|-------------------|---------------------------------------|-------------------|---------------------|

|                                      | ~ .               |                                       |                   |                     |

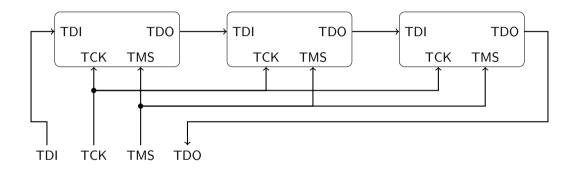

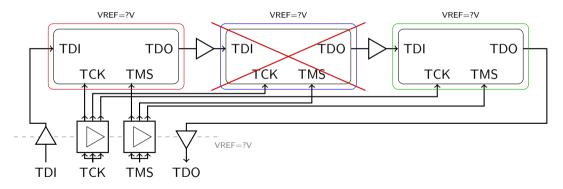

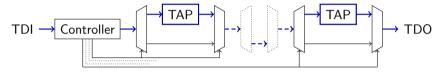

# Simple Daisy-Chain

- A Daisy-Chain is formed by connecting TDO to TDI of the next TAP controller

- TCK & TMS are shared signals

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher                        | Advanced Features | FPGA Implementation |

|----------------------------|-------------|--------------------------------------|-------------------|---------------------|

| 00000                      | 00          | 000000000000000000000000000000000000 | 00000000          |                     |

|                            |             |                                      |                   |                     |

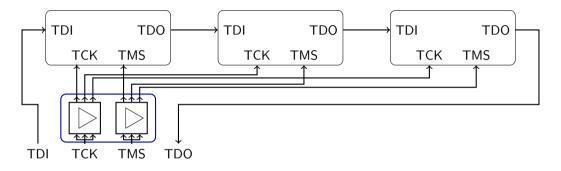

# Simple Daisy-Chain

#### Recommendation

Do not route TCK/TMS as a STAR (stub wires cause reflections). Use a buffer with one output per TAP for signal integrity.

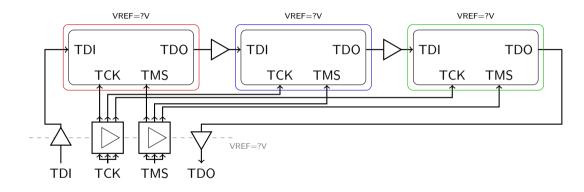

# Real world Daisy-Chain

• In case of different I/O Voltages multiple level shifters are required

<□> <同> <同> < 目> < 目> < 目> < 目> < 目> □ ○ ○ ○

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher                           | Advanced Features | FPGA Implementation |

|----------------------------|-------------|-----------------------------------------|-------------------|---------------------|

| 000000                     | 00          | 000000000000000000000000000000000000000 | 0000000           | 000                 |

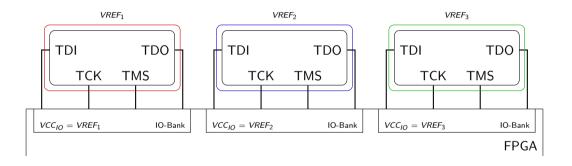

# **FPGA** Implementation

• IO-Banks of a (small) FPGA may be also used as level shifters

・ロト・(四ト・(川下・(日下・(日下)))

JTAG Daisy-Chaining Basics Limitations of Advanced Features of Advanced

## **FPGA** Implementation

#### Listing 1: Daisy-Chain VHDL

oTDI1 <= iTDI; -- TDI from probe to first TAP oTDI2 <= iTD01; oTD3 <= iTD02; oTD0 << iTD03; -- TD0 from last TAP to probe -- wire TCK as a STAR oTCK1 <= iTCK; oTCK2 <= iTCK; oTCK3 <= iTCK; -- wire TMS as a STAR oTMS1 <= iTMS; oTMS2 <= iTMS; oTMS3 <= iTMS;</pre>

| JTAG Daisy-Chaining Basics<br>00000● | Limitations<br>00 | JTAG Switcher<br>0000000000000000000000000 | Advanced Features | FPGA Implementation |

|--------------------------------------|-------------------|--------------------------------------------|-------------------|---------------------|

| Daisy-Chaining                       |                   |                                            |                   |                     |

- $\bullet\,$  JTAG Daisy-Chaining is simple as long as traces are short and the I/O Levels are matching

- The TCK (=Clock) Signal must have proper integrity

⇒ use single buffer, use one output per TAP to avoid stubs

- Having multiple I/O Levels requires level shifters  $\Rightarrow$  influences maximum TCK frequency

- The slowest TAP controller limits the maximum TCK frequency of the complete system

- All TAP controllers must be always functional

- $\Rightarrow$  next slide

| JTAG Daisy-Chaining Basics | Limitations<br>●○ | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

| Problem                    |                   |                                       |                   |                     |

• If one TAP controller is inaccessible the complete Daisy-Chain is broken

| JTAG Daisy-Chaining Basics | Limitations<br>⊙● | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

|                            |                   |                                       |                   |                     |

## Failure Situations

Scenarios that may trigger this problem

- SoC internal or Board level power-saving

- Redundant systems may power down

- CHIP-SECURITY

- A Secure boot must be never corrupted

- JTAG is an attack possibility already in early bootstages

- Some SoCs disable JTAG while booting completely e.g. JTAG pins tristated

- Some SoCs modify their internal daisy-chain while booting

- Some SoCs offer possibilities to disable JTAG with FUSEs

- most times not *properly* documented

- ⇒ We might lose control over early-stage debugging (Flash programming)

⇒ We might be locked out completely in later product lifecycles

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>•000000000000000000000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|--------------------------------------------------------|-------------------|---------------------|

| Overview                   |                   |                                                        |                   |                     |

## JTAG Daisy-Chaining Basics

#### 2 Limitations

- JTAG Switcher

- Static Chaining

- Dynamic Chaining

- Advanced FeaturesTDOSYNC

- STEALTH

- 5 FPGA Implementation

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher                           | Advanced Features | FPGA Implementation |

|----------------------------|-------------|-----------------------------------------|-------------------|---------------------|

|                            |             | 000000000000000000000000000000000000000 |                   |                     |

|                            |             |                                         |                   |                     |

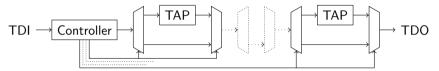

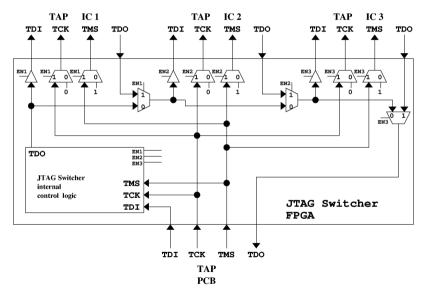

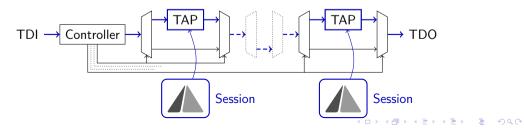

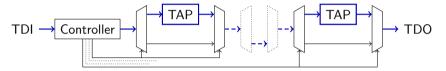

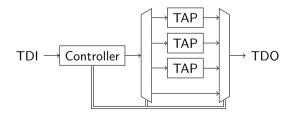

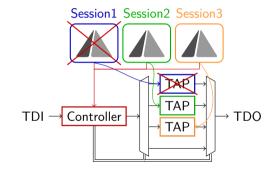

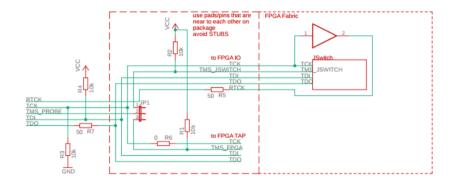

# JTAG Switcher Principle

• A possible solution is to mux-in/mux-out malicious/unused TAP controllers from the chain

# JTAG Switcher Principle

• A possible solution is to mux-in/mux-out malicious/unused TAP controllers from the chain

• Example: Select only last TAP, first TAP in error state

#### Schematical view of the JTAG Switcher FPGA IP

◆□▶ ◆□▶ ◆三▶ ◆三▶ ● ● ● ●

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher       | Advanced Features | FPGA Implementation |

|----------------------------|-------------|---------------------|-------------------|---------------------|

| 000000                     | 00          | ○○○●○○○○○○○○○○○○○○○ | 00000000          |                     |

| Static Chaining            |             |                     |                   |                     |

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Static Chaining            |                   |               |                   |                     |

Problem:

◆□ → ◆□ → ◆三 → ◆三 → ● ● ● ● ●

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Static Chaining            |                   |               |                   |                     |

Problem:

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Static Chaining            |                   |               |                   |                     |

Problem:

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Static Chaining            |                   |               |                   |                     |

## PRO

- Probe requires only Daisy-Chaining support

- $\Rightarrow \mathsf{wide \ tool \ support}$

- Industry standard technique

## CON

- Configuration needs to be written manually e.g. SVF, TRACE32 RemoteAPI, JTAG.SHIFT, JTAG.SEQuence

- Not robust against dynamic errors of TAPs

- Performance limitation depending on Daisy-Chain length and TAP performance

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher                           | Advanced Features | FPGA Implementation |

|----------------------------|-------------|-----------------------------------------|-------------------|---------------------|

|                            |             | 000000000000000000000000000000000000000 |                   |                     |

|                            |             |                                         |                   |                     |

# Usage

A JtagSwitc... B::SYStem.DETECT.SHOWChain - -O refresh 2 SYStem debug port pre / post PORT1 TDOSYNC No PORT/TAP selected Device Name IDCODE IRPRE IRPOST DRPRE DRPOST TDOSYNC PORT2 TDOSYNC PORT3 PORT4 TDOSYNC PORTS PORTO PORTZ TDOSYNC B::SYStem.DETECT.SHOWChain PORTS 🔥 JtagSwitc... PORTO TDOSYNC Q refresh 2 SYStem debug port pre / post PORT1 TDOSYNC First PORT/TAP selected PORT10 TDOSYNC Device Name JTAG Switcher ARM JTAG-DP DAP IDCODE 0x11111fff 0x4ba00477 IRPRE PORT2 TDOSYNC 1. 0. 0. 1. PORT11 4. 0. PORT3 TDOSYNC PORT12 TDOSYNC PORT4 TDOSYNC PORT13 TDOSYNC PORTS TROSYNC PORT14 TDOSYNC PORT15 PORT7 TDOSYNC PORT16 PORT/TAP TDOSYNC B:SYStem DETECT.SHOWChain A JtagSwitc.. STEALTH TDOSYNC Q refresh SYStem debug port pre / post PORT1 TDOSYNC Ful Reset Write Config TROSYNC Device Name 1 & 2 IDCODE 0x111111FFF PORT2 TDOSYNC SHOWChain PORT3 TDOSYNC ARM JTAG-DP DAP 0x4ba00477 Lattice MachX0 LCMX02280 0x0128d043 PORT12 TDOSYNC TDOSYNC selected PORT4 PORT13 TDOSYNC PORTS PORT14 TDOSYNC PORT6 PORT15 TDOSYNC TDOSYNC PORTZ Dialog for interactive Usage PORT16 TDOSYNC TDOSYNC PORTS STEALTH PORTO TDOSYNC Ful Reset Write Config part of JTAG Switcher download PORT10 SHOWChain TDOSYNC PORT11 PORT12 TDOSYNC DO <...>/lb cmm/jswitch dialog.cmm PORT13 PORT14 PORT15 PORT16 STEALTH Ful Reset Write Config

SHOWChain

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

|                            |                   |               |                   |                     |

## Usage

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>००० <b>००००</b> ●० <b>०</b> ००००००००० | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|--------------------------------------------------------|-------------------|---------------------|

| Examples                   |                   |                                                        |                   |                     |

## • Example: Enable PORT1

JTAG.SEQuence.Execute TLRJSwitchDisableAll JTAG.SEQuence.Execute TLRJSwitchWriteAllBanks 0x1 0x1 0x0 or (including disable all other ports pattern) JTAG.SEQuence.Execute TLRJSwitchWriteAllBanks 0x1 0x1|0xAAA8 0xAAAA

#### TLRJSwitchDisableAll

The JTAG Sequences TLRJSwitchDisableAll & TLRJSwitchReset are robust against 128 (remaining) IR-Bits in the chain (~32 ARM-SoCs).

#### **TLRJSwitchWriteAllBanks**

All JTAG Sequences TLRJSwitchWrite... must not be called when a debug session is active. The chain must include *ONLY* JTAG Switcher.

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Examples                   |                   |               |                   |                     |

• Example: Enable PORTs 4,5,9

JTAG.SEQuence.Execute TLRJSwitchDisableAll JTAG.SEQuence.Execute TLRJSwitchWriteAllBanks 0x1 0x140 0x1

- Example: Reset JTAG Switcher including all miscellaneous registers JTAG.SEQuence.Execute TLRJSwitchReset

- Example: Enable PORTs 4,5,9 enable TDOSYNC for Port 4,5 JTAG.SEQuence.Execute TLRJSwitchDisableAll JTAG.SEQuence.Execute TLRJSwitchWriteAllBanks 0x2 0x140 0x2 JTAG.SEQuence.Execute TLRJSwitchWriteAllBanks 0x1 0x140 0x1

#### Reminder

TLRJSwitchDisableAll does only reset the SELECT(=0x1) register, others e.g. TDO-SYNC(=0x2) are not affected.

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| 1.1                        |                   |               |                   |                     |

# Usage

#### Debug Session configuration

SYStem.CPU <SoC-Cluster> SYStem.CONFIG IRPRE <> SYStem.CONFIG DRPRE <> SYStem.CONFIG IRPOST <> SYStem.CONFIG DRPOST <> SYStem.Mode <Attach|Up>

#### ARM Coresight based System

SYStem.CDU <SoC-Cluster> SYStem.CONFIG DAPIRPRE <> SYStem.CONFIG DAPDRPRE <> SYStem.CONFIG DAPDRPOST <> SYStem.CONFIG DAPDRPOST <> SYStem.Mode <Attach Up>

| B::SYStem.DETECT.SHOWCh    | ain                |           |            |       |        | × |

|----------------------------|--------------------|-----------|------------|-------|--------|---|

| 📿 refresh 🖉 🖉 SYStem 🛛 deb | ug port) pre       | / post    |            |       |        |   |

| Device Name                | IDCODE             | IRPRE     | IRPOST     | DRPRE | DRPOST |   |

| JTAG Switcher              | 0x11111fff         | 12.       | 0.         | 2.    | 0.     | ~ |

| ARM JTAG-DP DAP            | <u> 0x4ba00477</u> | 8.        | 4.         | 1.    | 1.     |   |

| Lattice MachXO LCMX02280   | Set PRE            | / POST fo | r          |       | 2.     | Ŧ |

|                            | DAP                | N         |            |       | •      |   |

|                            | DAP2               | 43        |            |       |        |   |

|                            | RTP                |           |            |       |        |   |

|                            | NEXT               |           |            |       |        |   |

|                            | CHIP               |           |            |       |        |   |

|                            | Ø View PR          | E / POST  | settings   |       |        |   |

|                            | 💥 Clear all        | PRE / PO  | ST setting | s     |        |   |

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Dynamic Chair              | ning              |               |                   |                     |

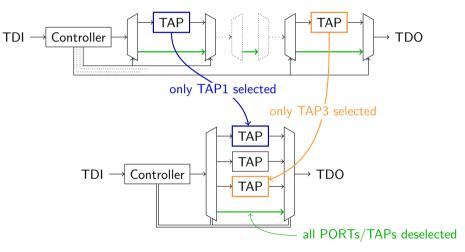

Usecase 2: Dynamically control the Daisy-Chain from the probe

- Idea: Activate only one PORT/TAP at a time

- $\bullet\,\Rightarrow$  Chain consists only of JTAG Switcher and current TAP of interest

- $\bullet\,\Rightarrow\, {\sf Errors}$  from other TAPs do not propagate

- Thus we may use JTAG Switcher as one logical multiplexer

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

| 000000                     | 00          | 000000000000000000000000000000000000000 | 00000000          | 000                 |

|----------------------------|-------------|-----------------------------------------|-------------------|---------------------|

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher                           | Advanced Features | FPGA Implementation |

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Dynamic Chain              | ing               |               |                   |                     |

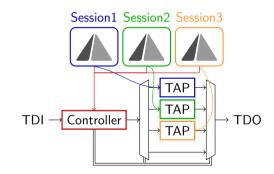

- Every Debug session connects (ideally) to only one TAP

- The probe (e.g. TRACE32) needs also to control the JTAG Switcher

- ⇒ We can dynamically start debug-sessions without prior Daisy-Chain configuration

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

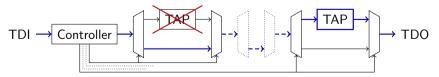

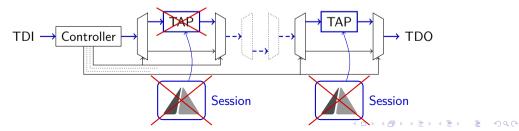

| Dynamic Chain              | ing               |               |                   |                     |

- In case one TAP has an (unlikely) error while the communication is active only this session is affected

- Example: TAP 1 in error state

- $\Rightarrow$  Session 2 & Session 3 remain active

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Dynamic Chai               | ning              |               |                   |                     |

## PRO

- No *pre-initialization* required, configuration can be written by probe on demand

- We can dynamically add sessions

- Speed limitiations (maximum TCK) of one TAP does not propagate

- Better performance due to shorter Daisy-Chain length

## CON

• Probe requires support for JTAG Switcher

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Dynamic Chai               | ning              |               |                   |                     |

#### Sequence - initial Connect

(TRACE32: SYStem.CONFIG.MULTITAP JtagSEQuence Attach)

- Bring possible remaining Daisy-Chained TAPs into a safe state (JTAG BYPASS)

- Disable all possibly activated JTAG Switcher PORTs (Reset all SELECT registers=0x7)

optional Write JTAG Switcher miscellaneous configuration registers (e.g. TDOSYNC)

- Write SELECT Register (Set Bit) and apply configuration

- Test-Logic-Reset of Slave-Port-TAP

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Dynamic Chai               | ning              |               |                   |                     |

Sequence - activate PORT

Б

(TRACE32: SYStem.CONFIG.MULTITAP JtagSEQuence SELect)

- Write SELECT Register (Set Bit) and apply configuration

- Probe operation ...

Sequence - deactivate PORT

(TRACE32: SYStem.CONFIG.MULTITAP JtagSEQuence DeSELect)

• Probe operation ...

either Disable all activated JTAG Switcher PORTs (Reset all SELECT registers=0x7)

or Write SELECT Register (Clear Bit) and apply configuration

# Dynamic Chaining - TRACE32

Usage:

```

SYStem.CPU <SoC-Cluster>

DO <...>/lb_cmm/jswitch_multitap_jtagsequence.cmm PORT=<x>

SYStem.Mode <Attach|Up>

```

The script jswitch\_multitap\_jtagsequence.cmm patches all required settings to control JTAG Switcher into the current TRACE32 session.

| 🔑 B::SYStem.0      | CONFIG /MultiTap  |                  |                  |

|--------------------|-------------------|------------------|------------------|

| DebugPort          | Jtag MultiTap     | AccessPorts COmp | onents           |

| - MULTITAP<br>NONE | 0                 |                  |                  |

| JtagSEQuence       | List available JT | AG sequences     |                  |

|                    | Attach            | SELect           | DeSELect         |

|                    | JSwitchAttach 🔹   | JSwitchEnable 🔻  | JSwitchDisable 🔻 |

|                    |                   |                  |                  |

|                    |                   |                  |                  |

|                    |                   |                  |                  |

|                          | _          |              | ×    |

|--------------------------|------------|--------------|------|

| 🗶 Delete All 🛛 😰 Store 🤇 | Load 🗎 🕇 🤇 | reate Sequen | ce   |

| JTAG Sequence            | state      | owner        |      |

| JSwitchAttach            | locked     | user         |      |

| JSwitchDisable           | locked     | user         |      |

| JSwitchDisableWithReset  | idle       | user         |      |

| JSwitchEnable            | locked     | user         |      |

| JSwitchReset             | idle       | user         | Ŧ    |

| •                        |            |              | ۱. H |

・ロト・日本・日本・日本・日本

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Examples                   |                   |               |                   |                     |

#### Example: STM32F103 on Port 1

SYStem.CPU STM32F103 DO <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=1 SYStem.Mode <Attach|Up>

#### Example: STM32F103 on Port 1, activate TDOSYNC

SYStem.CPU STM32F103 D0 <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=1 TDOSYNC SYStem.Mode <Attach|Up>

# Example: Daisy-Chain on Port 1 JTAG Switcher -> FPGA (IR=5, DR=1) -> STM32F103 -> JTAG Switcher

SYStem.CPU STM32F103 D0 <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=1 IRPOST=5 DRPOST=1 SYStem.Mode <Attach|Up>

・ロト・日本・日本・ 日本・ 日本・ 日本

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------|-------------------|---------------------|

| Examples                   |                   |               |                   |                     |

#### Example: Daisy-Chain on Port 5 JTAG Switcher -> STM32F103 -> FPGA (IR=5, DR=1) -> JTAG Switcher

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

SYStem.CPU STM32F103 DO <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=5 IRPRE=5 DRPRE=1 SYStem.Mode <Attach|Up>

#### Example: ZYNQ-Ultrascale+ on Port 4 JTAG Switcher -> SoC internal Daisy-Chain -> JTAG Switcher

SYStem.CPU ZYNQ-ULTRASCALE+-APU DO <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=4 IRPOST=12 DRPOST=1 SYStem.Mode <Attach|Up>

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features<br>●○○○○○○○ | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------------------|---------------------|

| Overview                   |                   |                                       |                               |                     |

▲□▶ ▲□▶ ▲□▶ ▲□▶ ▲□ ● のへで

## JTAG Daisy-Chaining Basics

#### 2 Limitations

C V V

- 3 JTAG Switcher

- Static Chaining

- Dynamic Chaining

- Advanced Features

TDOSYNC

STEALTH

5 FPGA Implementation

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

| TDOSYNC                    |                   |                                       |                   |                     |

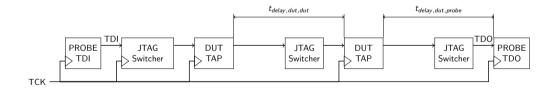

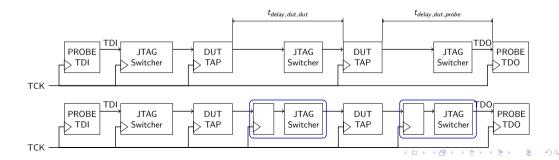

- Simplified timing model of a JTAG Switcher Daisy-Chain with two Slave TAPs/PORTs activated

- Two worst case timings t<sub>delay,dut,dut</sub> and t<sub>delay,dut,probe</sub> Includes: level shifters, signal lines and delay in Slave TAP & FPGA

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

| 000000                     | 00          |               |                   | 000                 |

|----------------------------|-------------|---------------|-------------------|---------------------|

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher | Advanced Features | FPGA Implementation |

# TDOSYNC

- Simplified timing model of a JTAG Switcher Daisy-Chain with two Slave TAPs/PORTs activated

- Two worst case timings t<sub>delay,dut,dut</sub> and t<sub>delay,dut,probe</sub>

Includes: level shifters, signal lines and delay in Slave TAP & FPGA

- $\Rightarrow$  TDOSYNC adds a synchronization register (virtual IR/DR Bit)

JTAG Daisy-Chaining Basics Limitations JTAG Switcher Advanced Features PPGA Implementation

# **TDOSYNC Static Chaining**

- TDOSYNC is available in the JTAG Switcher Dialog

- TDOSYNC can also be activated using the jswitch\_jtag\_sequence\_lib.cmm & JTAG.SEQuence.Execute compare examples in Static Chaining section

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

• The inserted TDOSYNC register needs to be configured in the SYStem.CONFIG [DAP]IRPRE SYStem.CONFIG [DAP]DRPRE JTAG Daisy-Chaining Basics Limitations JTAG Switcher Advanced Features PPGA Implementation

# **TDOSYNC Static Chaining**

- TDOSYNC is available in the JTAG Switcher Dialog

- TDOSYNC can also be activated using the jswitch\_jtag\_sequence\_lib.cmm & JTAG.SEQuence.Execute compare examples in Static Chaining section

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

• The inserted TDOSYNC register needs to be configured in the SYStem.CONFIG [DAP]IRPRE SYStem.CONFIG [DAP]DRPRE

# **TDOSYNC Static Chaining**

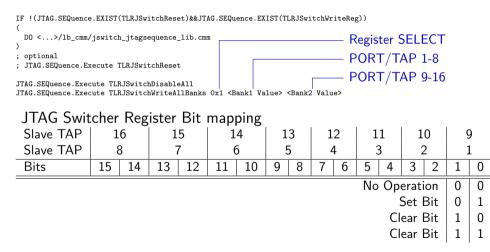

#### Example: enable PORT 1 with STM32F103, activate TDOSYNC

```

IF !(JTAG.SEQuence.EXIST(TLRJSwitchReset)&&JTAG.SEQuence.EXIST(TLRJSwitchWriteReg))

```

```

DO <...>/lb_cmm/jswitch_jtagsequence_lib.cmm

```

```

: optional

```

```

; JTAG.SEQuence.Execute TLRJSwitchReset

```

JTAG.SEQuence.Execute TLRJSwitchbriteAllBanks 0x2 0x1 ; TDOSYNC JTAG.SEQuence.Execute TLRJSwitchWriteAllBanks 0x2 0x1 ; SELECT

SYStem.COV STM32F103 SYStem.CONFIG DAPIRPOST 4. ; JTAG Switcher SYStem.CONFIG DAPDRPOST 1. ; JTAG Switcher SYStem.CONFIG DAPIRPRE 1. ; TDOSYNC SYStem.CONFIG DAPDRPRE 1. ; TDOSYNC SYStem.Mode <AttachlUp>

▲□▶▲□▶▲□▶▲□▶ ▲□ ● のへで

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ の00

# **TDOSYNC** Dynamic Chaining

- TDOSYNC is available as a parameter in DO <...>/lb cmm/jswitch multitap jtagsequence.cmm

- Daisy-Chaining paramters are automatically calculated

#### Example: enable PORT 1 with STM32F103, activate TDOSYNC

SYStem.CPU STM32F103 D0 <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=1 TDOSYNC SYstem.Mode <Attach|Up>

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features<br>○○○○○●○ | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|------------------------------|---------------------|

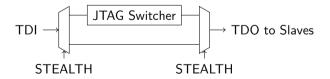

| STEALTH Mo                 | de                |                                       |                              |                     |

- Some SoCs require to be *first* in chain

- Examples: TriCore, C166, possibly others

- In order to daisy-chain these devices, STEALTH mode hides JTAG Switcher in the Daisy-Chain

- $\Rightarrow\,$  First enabled PORT becomes first in chain

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features<br>○○○○○○● | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|------------------------------|---------------------|

| STEALTH Usa                | ge                |                                       |                              |                     |

#### Static-Chaining: enable PORT 1 with STM32F103, activate STEALTH

```

IF !(JTAG.SEQuence.EXIST(TLRJSwitchReset)&&JTAG.SEQuence.EXIST(TLRJSwitchWriteReg))

(

D0 <...>/lb_cmm/jswitch_jtagsequence_lib.cmm

)

; optional

; JTAG.SEQuence.Execute TLRJSwitchReset

```

```

JTAG.SEQuence.Execute TLRJSwitchDisableAll

JTAG.SEQuence.Execute TLRJSwitchWriteAllBanksStealth 0x1 0x1 ; SELECT + STEALTH

```

SYStem.CPU STM32F103 SYStem.Mode <Attach|Up>

#### Dynamic-Chaining: enable PORT 1 with STM32F103, activate STEALTH

SYStem.CPU STM32F103 DO <...>/lb\_cmm/jswitch\_multitap\_jtagsequence.cmm PORT=1 STEALTH SYStem.Mode <Attach|Up>

| JTAG Daisy-Chaining Basics | Limitations<br>00 | JTAG Switcher<br>00000000000000000000 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|---------------------------------------|-------------------|---------------------|

| Overview                   |                   |                                       |                   |                     |

## **1** JTAG Daisy-Chaining Basics

#### 2 Limitations

- 3 JTAG Switcher

- Static Chaining

- Dynamic Chaining

- Advanced Features

- TDOSYNC

- STEALTH

## 5 FPGA Implementation

| JTAG Daisy-Chaining Basics | Limitations<br>00 | Advanced Features | FPGA Implementation |

|----------------------------|-------------------|-------------------|---------------------|

|                            | /                 |                   |                     |

- VHDL Source available under MIT License

- Tested on Lattice MachXO/iCE40/ECP5, Altera MAX V/10, Xilinx CoolRunner

- IP is configured using a single VHDL file jswitch\_config\_pkg.vhd

▲□▶ ▲□▶ ▲ □▶ ▲ □▶ ▲ □ ● ● ● ●

• Source: https://www.lauterbach.com/jtag\_switcher.html

| JTAG Daisy-Chaining Basics | Limitations | JTAG Switcher | Advanced Features | FPGA Implementation |

|----------------------------|-------------|---------------|-------------------|---------------------|

|                            |             |               |                   | 000                 |

#### Example to share JTAG probe connector between FPGA and JTAG Switcher

◆□ > ◆□ > ◆ Ξ > ◆ Ξ > → Ξ = の < @